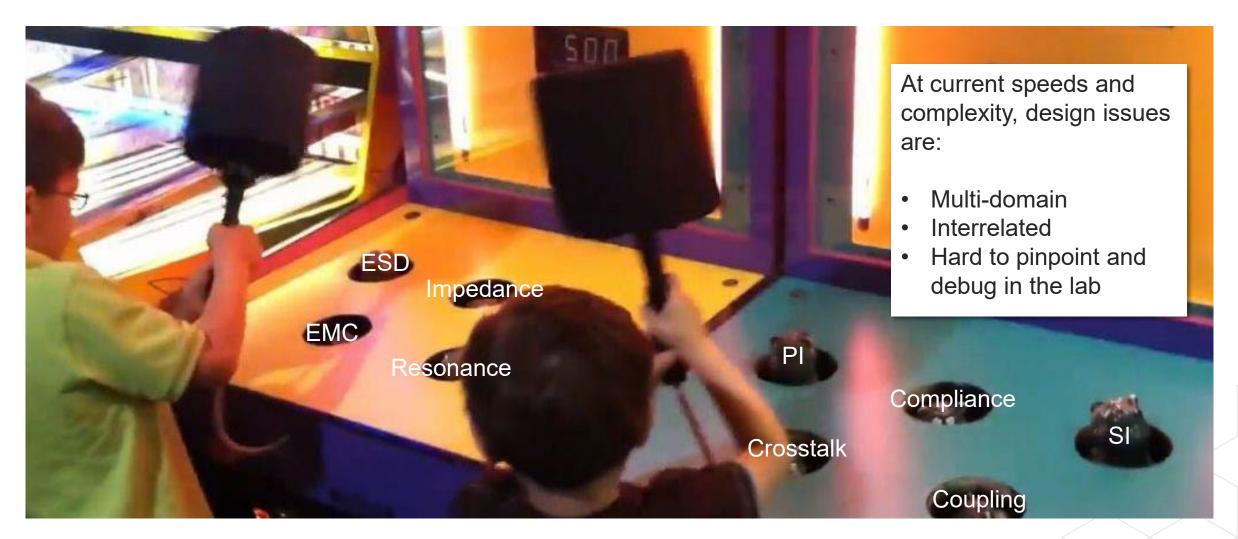

# Design Challenges Whack-a-Mole

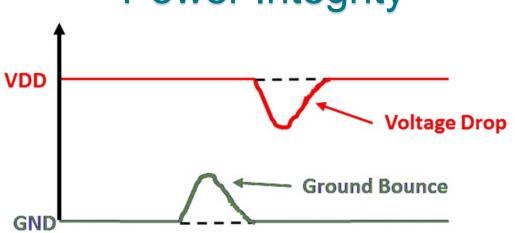

# **Power Integrity**

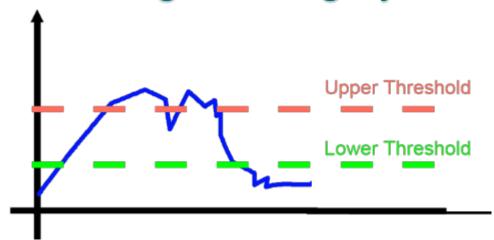

# Signal Integrity

cādence

#### Signal Integrity:

Reflection noise

Terminations and routing topologies

Cross talk

Attenuation and loss

Mode conversion

#### Signal Path

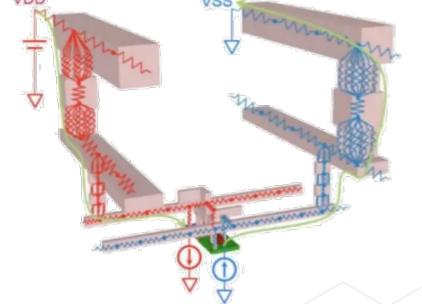

#### SI/PI:

Power rail noise induced jitter Power supply noise coupling Signal to cavity coupling Cavity to signal coupling Reducing cavity impedance

#### SVPVEMI:

Return path discontinuities

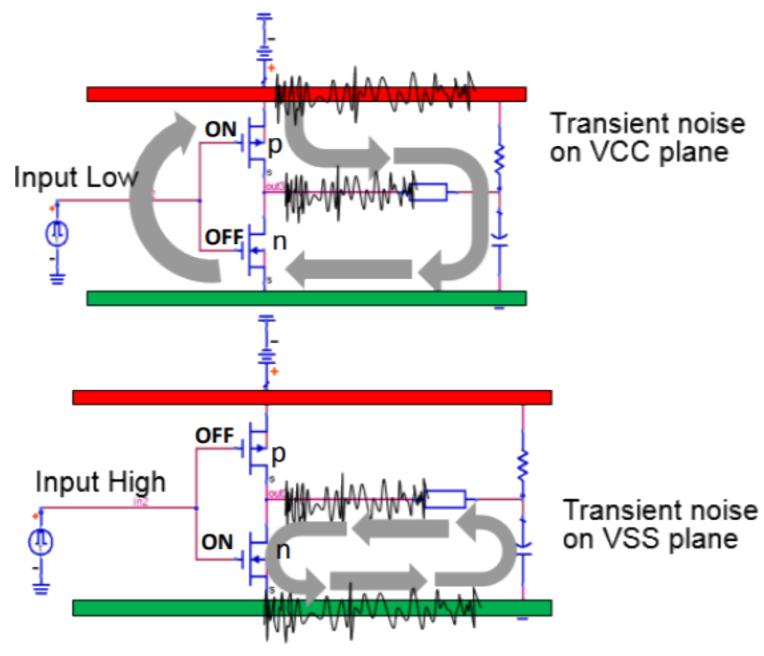

Ground bounce

Cavity impedance and resonances

Cable coupling to the edge of boards

Signal routing near the edge of boards

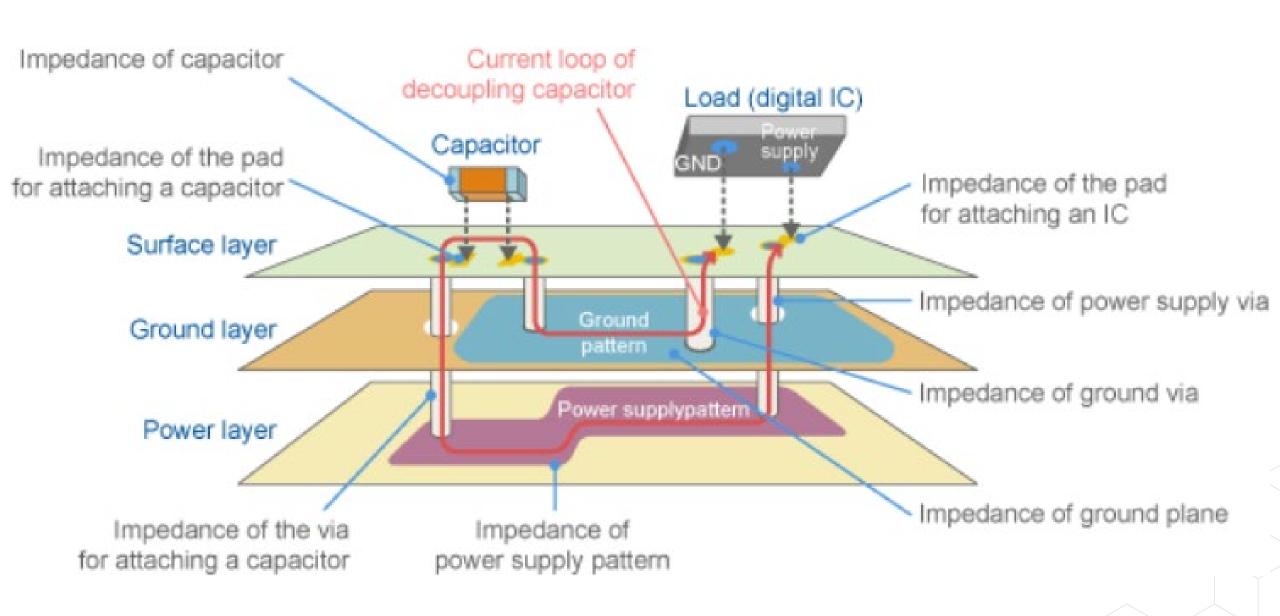

Return vias and decoupling capacitors

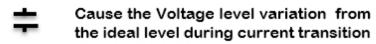

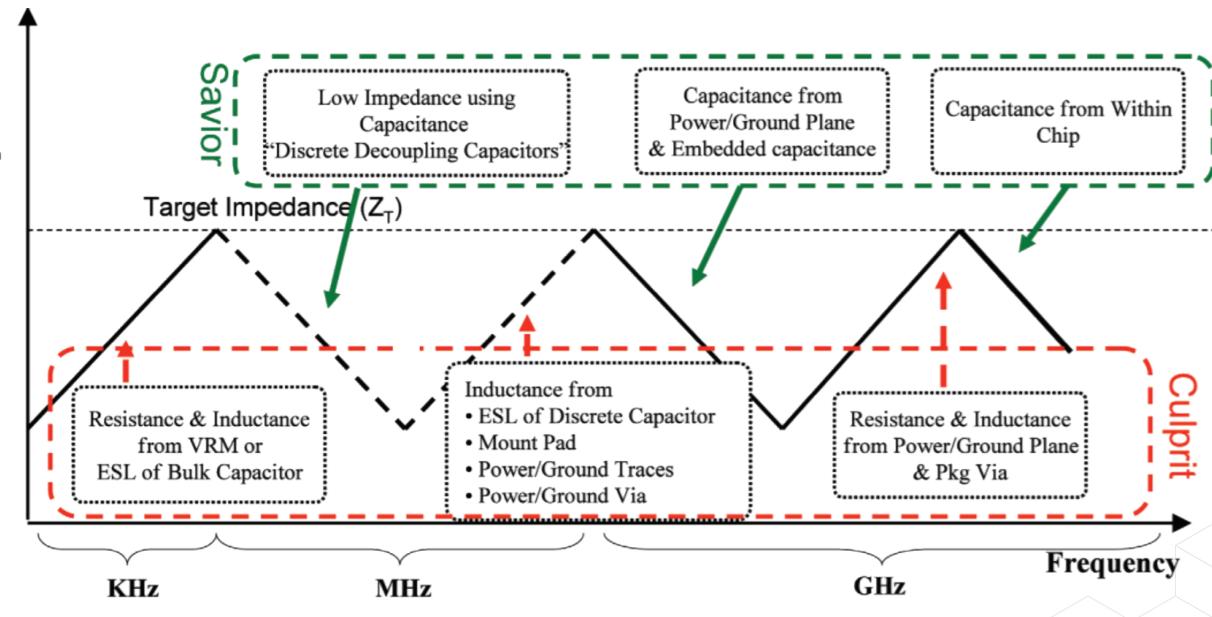

#### Power Integrity: Core logic voltage noise

On-die capacitance

Bandini Mountains

Package power path loop inductance

On-package capacitors

Controlled ESR capacitor

Decoupling capacitor integration

and selection

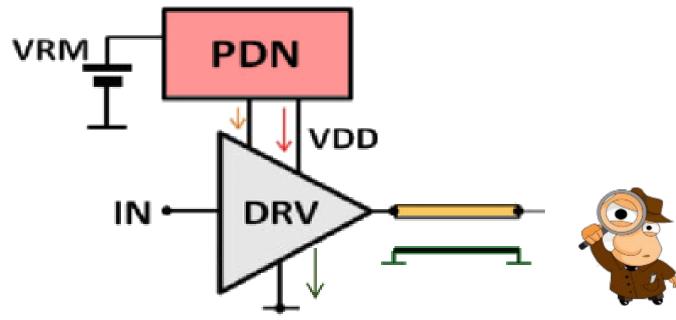

Power Delivery Path

#### SI/EMC:

Mode conversion and common currents

Common mode chokes in connectors

Board to board near field coupling

SSCG and phase lock loops

Cable, connector design and EMI/EMC

#### PI/EMC:

Cavity resonances

Radiation from the edge of boards

Power supply design and large

current transients

Common currents in power lines

(conducted emissions)

Power line filters

#### EMC/EMI:

Conducted emissions

Common currents

Antenna design (on purpose and accidental)

Near field effects vs far field effects

SSCG

Common mode chokes

Radiated Path

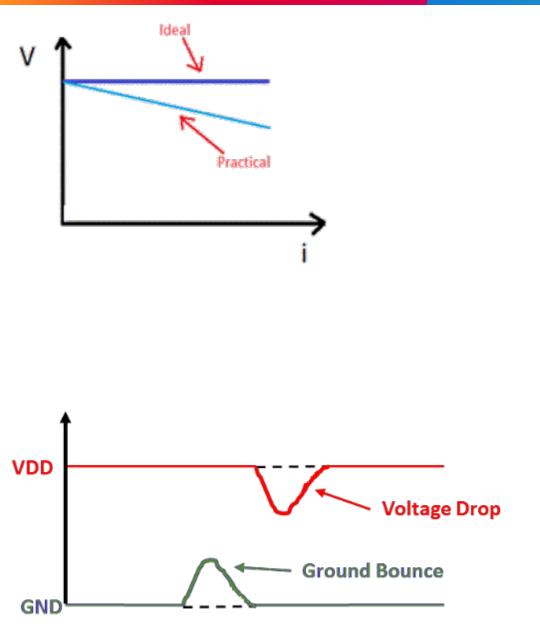

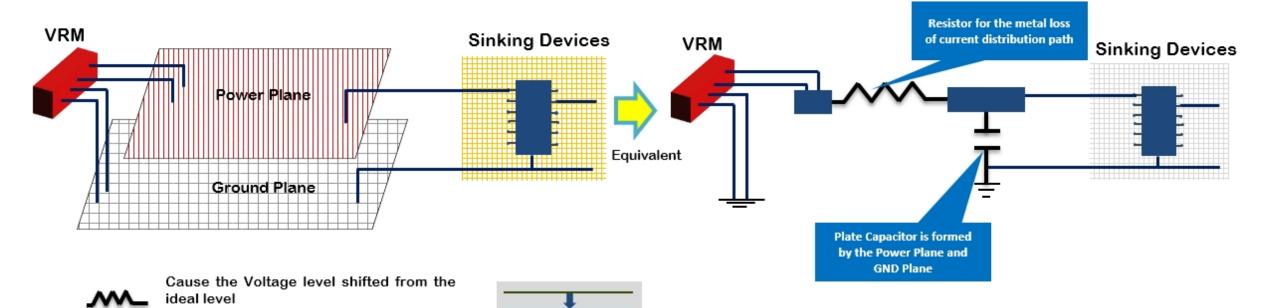

- Voltage Drop

- · Current Densities

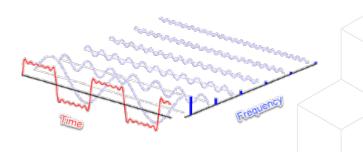

We Need AC Analysis (Dynamic IR Drop)

- Decoupling / Target Impedance

- Plane Noise

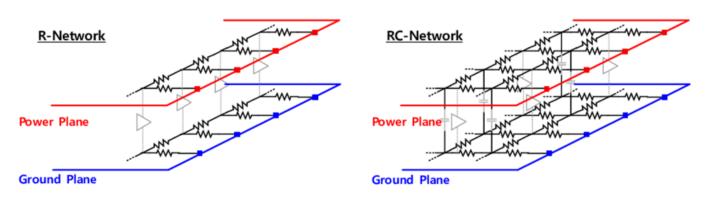

From the electrical point of view, the goal in designing a PDN is simple to describe: minimize the impedance between power and ground for the appropriate frequency range

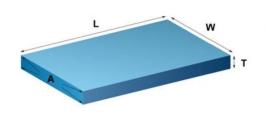

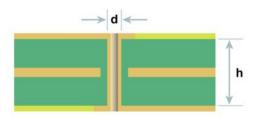

## Power Plane Resistance - Squares method

$$R = \frac{\rho L}{A} = \frac{\rho L}{WT}$$

$$\mathrm{R} = \frac{\rho L}{A} = \frac{\rho L}{WT} \qquad \qquad \mathrm{R}_{\mathrm{SQUARE}} = \frac{\rho \mathcal{L}}{\mathcal{L}T} = \frac{\rho}{T} \qquad \text{For a square of Copper W = L} \\ \mathrm{Resistance is independent of size}$$

R = Total resistance

A = Cross-sectional area of plane

T = Thickness, defined by copper weight

P = Resistivity of Copper, typically 1.7μΩ-cm (0.67μΩ-in) at 25°C

| Copper Weight oz | Thickness mm [mils] | mΩ/square at 25°C |

|------------------|---------------------|-------------------|

| 0.5              | 0.02 [0.7]          | 1.0               |

| 1                | 0.04 [1.4]          | 0.5               |

| 2                | 0.07 [2.8]          | 0.25              |

#### Via Resistance Current Flow Cross-sectional area Resistance of Via equivalent to resistance of trace with equivalent CSA and length $R = \frac{\rho L}{A}$ Plating Thickness $R = \frac{\rho L}{\pi (ro^2 - ri^2)}$ Hole Diameter Material μΩ-cm μΩ-in Copper 1.70 0.67 Copper (plated) 6.0 2.36 Gold 2.2 0.87

\*Note: resistivity of plated copper can be higher than pure copper; consult with PCB vendor

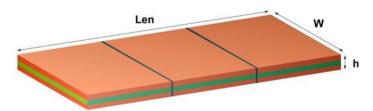

#### Power Plane Inductance – Rule of Thumb

$$L_{LOOP} = \mu_0 * h * \frac{Len}{W} = 32 \text{pH/mil} * h * \frac{Len}{W}$$

$$L_{LOOP} = \mu_0 * h * \frac{Len}{W}$$

$$\mu_{LOOP} = \mu_0 * h * \frac{Len}{W}$$

Inductance per square of two adjacent parallel power planes approximately 32pH per mil of dielectric Example: 3.1mil dielectric approximately 100pH per square\*

### Via Inductance

$$L_{via} = 5.08 h \left[ ln \left( \frac{4h}{d} \right) + 1 \right]$$

Where:

L<sub>via</sub> = inductance of via, nH

D = via diameter, in. H = length of via, in.

### $F_{MAX}$ $\setminus$ $Z_{TARGET}$ $|Z_{EFF}|$ Frequency 1MHz 50-100MHz 1-5KHz Power/Ground Mid -Electrolytic Bulk PMIC/VRM Inter-plane Frequency Capacitance Ceramic Capacitors Capacitors

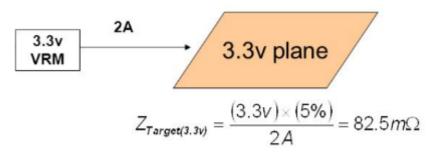

# **Target Impedance Calculation**

$$Z_{\textit{Target}} = \frac{(\textit{Power \_Supply\_Voltage}) \times (\textit{Allowed \_Ripple})}{\textit{Current}}$$

### Example:

Target Impendence is the goal!!!

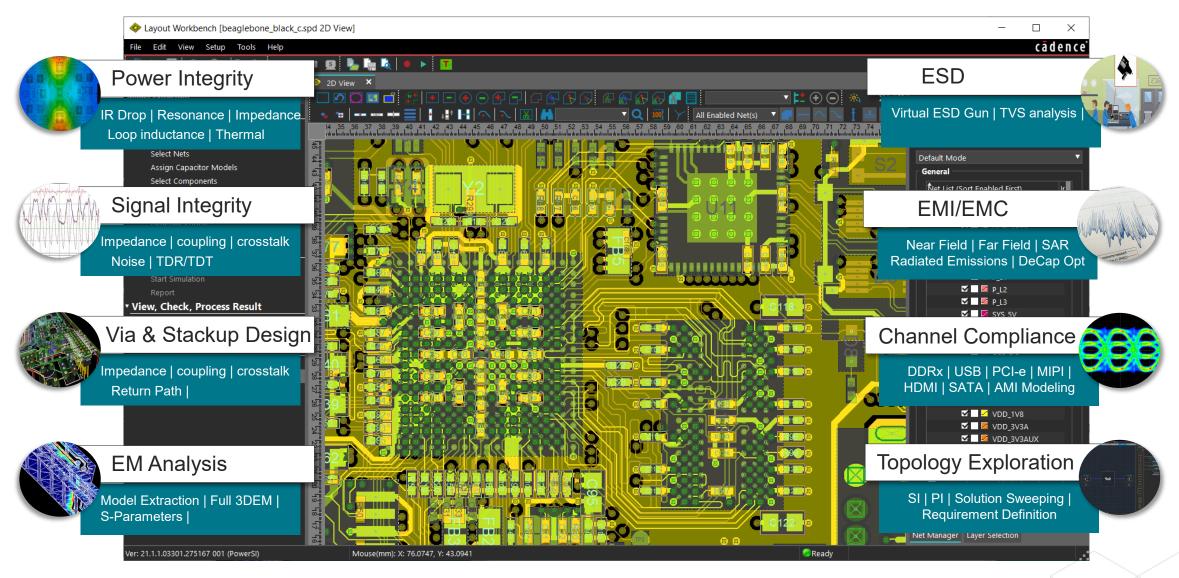

# Sigrity Unified Analysis WorkBench