# A Dive into DDR5: An Engineer's Guide to Simulating and Validating the Latest Generation of DDR

Stephen Newberry | Terry Jernberg Sept. 22, 2021

### **Meet the Presenter**

- Stephen Newberry:

- Signal Integrity Engineer at Astranis

- B.S. in ECE from Rutgers

- Former U.S. Coast Guard Electrician's Mate

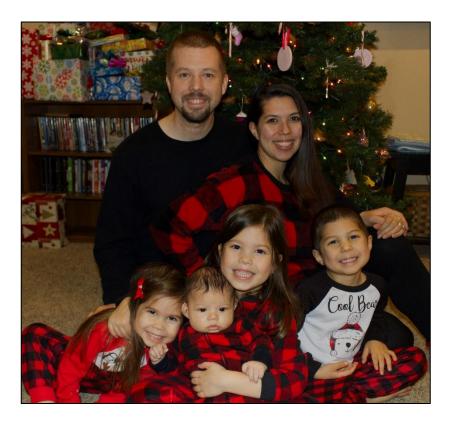

- Husband and father of 4

# **ASTRAN**S

# Introduction

- This overview has **two goals**:

- Provide **basic info** about DDR5 changes

- Introduce simulation with IBIS-AMI and DFE

- Intended audience:

- Familiar with prior DDR specifications

- Want to see the **major updates** in DDR5

- Jump into **simulation**

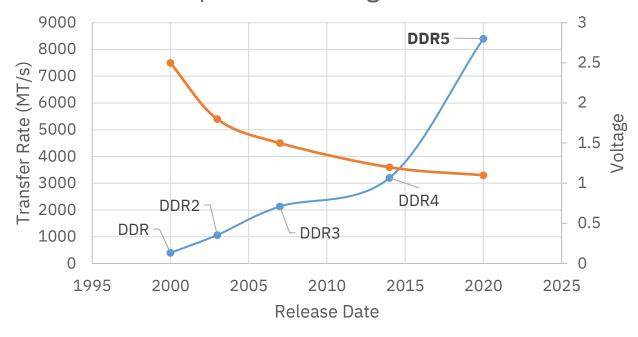

- DDR4 is fast

- DDR5 is *blazing*

- Tables in JESD79-5 have placeholder text to 8400 MT/s!

- Many clever features are employed to gain functionality

- Better but not significantly different basic architecture unchanged

- Not (yet) using differential signaling for data

- Package sizes and **pinouts** are similar

- Advances require **alternate approach** to simulation and analysis

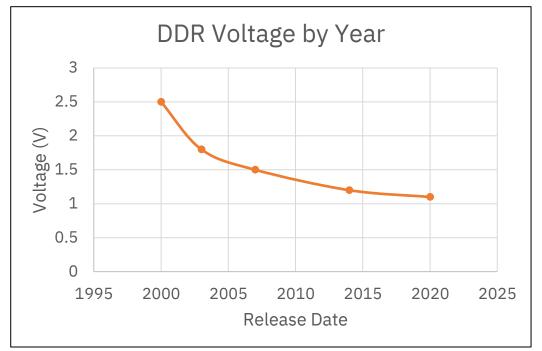

Transfer Rate Voltage

Data from Wikipedia: https://en.wikipedia.org/wiki/DDR\_SDRAM

#### Shield Digital Design

DDR Speed and Voltage over Time

# Outline

- 1. Major Changes from DDR4

- 1. Reduced VDD/VDDQ

- 2. CA Bus: Non-Specific Signal Names

- 3. CA Bus: Internal Vref

- 4. On-Die Termination Changes

- 2. New Features in DDR5

- 1. VRM on DIMM

- 2. Duty Cycle Adjuster

- 3. On-Die ECC

- 4. Decision Feedback Equalization

- 3. Simulation Example

- 1. Full byte lane with DFE

# **1. Major Changes from DDR4**

# VDD/VDDQ to 1.1V

- DDR4 was 1.2V

- Sequence: VPP then VDD/VDDQ

- Then RESET\_n

Data from Wikipedia: https://en.wikipedia.org/wiki/DDR\_SDRAM

- DC Operating Range: +6%/-3%

- On all VDD/VDDQ/VPP

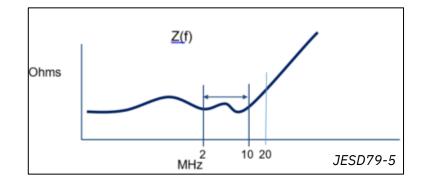

- PDN Impedance preliminary specification:

- + 10 m $\Omega$  from 2-10 MHz

- + 20 m $\Omega$  at 20 MHz

# CA Bus: Non-Specific Signal Names

- DDR4 used specific pins: ACT\_n, RAS\_n, CAS\_n, etc.

- DDR5 uses generic bus: CA[0..13]

- No pin-swapping allowed

- Commands may be multi-cycle

- But be aware of MIR pin (mirror) for clamshell configuration

- Internally swaps even CA pin with next highest odd CA

- Biggest impact to the designer?

- Easier schematic capture: simple bus connection

- Fewer CA pins mean more GND pins

- Improved return path = better signal integrity

| DDR5 command encoding <sup>[22][final standard verification needed]</sup> |    |                           |                                     |   |                      |      |         |                    |     |                     |        |       |             |       |              |

|---------------------------------------------------------------------------|----|---------------------------|-------------------------------------|---|----------------------|------|---------|--------------------|-----|---------------------|--------|-------|-------------|-------|--------------|

| Command CS                                                                |    | Command/address (CA) bits |                                     |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| Command                                                                   | 05 | 0                         | 1                                   | 2 | 3                    | 4    | 5       | 6                  | 7   | 8                   | 9      | 10    | 11          | 12    | 13           |

| Active (activate)                                                         | L  | L                         | L L Row R0–3 Bank Bank group Chip C |   |                      |      |         |                    |     |                     |        | p CID | 00-2        |       |              |

| Open a row                                                                | н  |                           | Row R4–16                           |   |                      |      |         |                    |     |                     |        |       |             |       | R17/<br>CID3 |

|                                                                           | L  | L                         | L H V                               |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| Unassigned, reserved                                                      | V  |                           |                                     |   |                      |      |         |                    |     |                     |        |       |             |       |              |

|                                                                           | L  | Н                         | H L L L V                           |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| Unassigned, reserved                                                      | Н  | V                         |                                     |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| 1017                                                                      | L  | н                         | L                                   | L | н                    | L    | Н       | Ba                 | ink | Bank group Chip CID |        |       |             |       | 0–2          |

| Write pattern                                                             | Н  | V                         |                                     |   | С                    | olun | nn C3–1 | 0                  |     |                     | V AP H |       |             |       | CID3         |

|                                                                           | L  | Н                         | H L L H H V                         |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| Unassigned, reserved                                                      | Н  | V                         |                                     |   |                      |      |         |                    |     |                     |        |       |             |       |              |

| Ande en eleter weite                                                      |    | Н                         | L                                   | н | H L L Address MRA0-7 |      |         |                    |     |                     |        | V     |             |       |              |

| Mode register write                                                       | Н  |                           |                                     | 0 | )ata                 | MR   | D0–7    |                    |     | ١                   | V      | CW    |             | V     |              |

| Made conjector cond                                                       | L  | Н                         | L                                   | н | L                    | н    |         | Address MRA0-7     |     |                     |        |       |             |       | V            |

| Mode register read                                                        | н  | V CW                      |                                     |   |                      |      | V       |                    |     |                     |        |       |             |       |              |

| 10/-1-                                                                    | L  | н                         | L                                   | н | н                    | L    | BL      | BL Bank Bank group |     |                     |        | Chi   | Chip CID0-2 |       |              |

| Write                                                                     | Н  | ۷                         |                                     |   | С                    | olun | nn C3–1 | 0                  |     |                     | ۷      | ĀP    | WRP         | V     | CID3         |

| Read                                                                      | L  | Н                         | L                                   | н | н                    | н    | BL      | Ba                 | ink | Ba                  | ank    | group | Chi         | p CID | 0–2          |

| кеаа                                                                      | н  | v                         |                                     |   | С                    | olur | nn C3–1 | 0                  |     |                     | v      | ĀP    | V           | V CII |              |

| Vref CA                                                                   | L  | Н                         | н                                   | L | L                    | L    |         |                    |     |                     | Data   | а     |             |       | V            |

Data table from Wikipedia: https://en.wikipedia.org/wiki/DDR5\_SDRAM

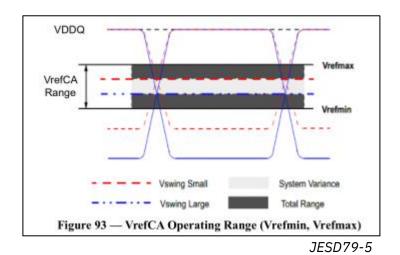

# **CA Bus Internal VREF**

- DDR4 used external VREFCA

- DDR5 has internally generated VREFCA

- Identical to VREFDQ

- Internally adjustable via register commands

- From 45% to 97.5% of VDDQ

- 0.5% increments

- Reduced PCB design requirements

- No VTT/VREF regulator needed

|   |   |         | Table 1 -                              | – DDR4 SD                | RAI | M X4 | I/8 E | allout using                                              | MO-207                                    |                          |   |

|---|---|---------|----------------------------------------|--------------------------|-----|------|-------|-----------------------------------------------------------|-------------------------------------------|--------------------------|---|

|   |   | 1       | 2                                      | 3                        | 4   | 5    | 6     | 7                                                         | 8                                         | 9                        |   |

| A |   | VDD     | VSSQ                                   | TDQS_c <sup>3</sup>      |     |      |       | DM_n, DBI_n<br>TDQS_t <sup>2</sup> ,<br>(NC) <sup>1</sup> | VSSQ                                      | vss                      |   |

| в |   | VPP     | VDDQ                                   | DQS_c                    |     |      |       | DQ1                                                       | VDDQ                                      | ZQ                       |   |

| С |   | VDDQ    | DQ0                                    | DQS_t                    |     |      |       | VDD                                                       | VSS                                       | VDDQ                     |   |

| D |   | VSSQ    | DQ4<br>(NC) <sup>1</sup>               | DQ2                      |     |      |       | DQ3                                                       | DQ5<br>(NC) <sup>1</sup>                  | vssq                     |   |

| E |   | VSS     | VDDQ                                   | DQ6<br>(NC) <sup>1</sup> |     |      |       | DQ7<br>(NC) <sup>1</sup>                                  | VDDQ                                      | vss                      |   |

| F |   | VDD     | (C2) <sup>5</sup><br>ODT1 <sup>6</sup> | ODT                      |     |      |       | CK_t                                                      | CK_c                                      | VDD                      |   |

| G |   | vss     | (C0) <sup>5</sup><br>CKE1 <sup>6</sup> | СКЕ                      |     |      |       | CS_n                                                      | (C1) <sup>5</sup><br>(CS1_n) <sup>6</sup> | TEN<br>(NC) <sup>7</sup> | ( |

| н |   | VDD     | WE_n<br>A14                            | ACT_n                    |     |      |       | CAS_n<br>A15                                              | RAS_n<br>A16                              | vss                      | 1 |

| J | Π | VREFCA  | BG0                                    | A10<br>AP                |     |      |       | A12<br>BC_n                                               | BG1                                       | VDD                      |   |

| κ | ٦ | vss     | BA0                                    | A4                       |     |      |       | A3                                                        | BA1                                       | VSS                      |   |

| L |   | RESET_n | A6                                     | A0                       |     |      |       | A1                                                        | A5                                        | ALERT_n                  |   |

| М |   | VDD     | A8                                     | A2                       |     |      |       | A9                                                        | A7                                        | VPP                      | 1 |

| N |   | vss     | A11                                    | PAR                      |     |      |       | A17<br>(NC) <sup>4</sup>                                  | A13                                       | VDD                      |   |

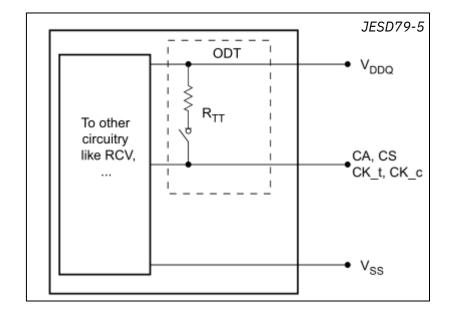

# **On-Die Termination Changes**

- All ODT is now fully command/register based

- No dedicated ODT pin

- ODT is now available for CA bus

- DQ/DQS still use direct routing from controller to DRAM

- CA bus uses fly-by routing

- Pin CA\_ODT allows different settings for end-of-group

- Could use  $40\Omega$  for end device but ODT disabled for other devices

# **2. New Features in DDR5**

# VRM on DIMM

- Excellent for power integrity

- DC (IR drop) and AC (PDN impedance)

#### • Four SMPS, three LDO

- 15W of power

- 4.25 15V input for SMPS, 3 3.6V input for LDO

- OV protection for SMPS input

- OV/UV/OC protection for SMPS output

- ADC for voltage, current, temp measurement

- Two management interfaces

- I2C or "I3C Basic"

- I3C is a MIPI modification of I2C (open-drain or push-pull, faster data rates)

- Same pins for both

| PMIC50x0 Po<br>Specification, | ower Management IC<br>Rev 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JESD301-1                     | 10<br>International International |

| JUNE 2020                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| JULE 2020                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

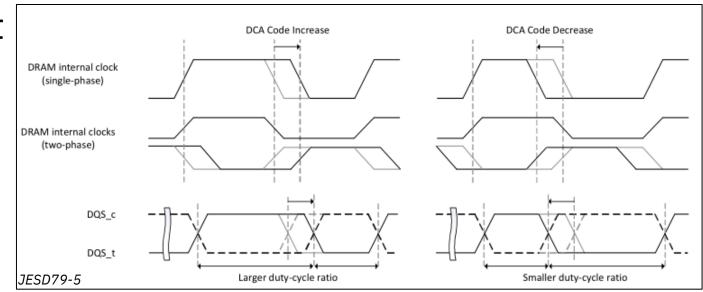

# **Duty Cycle Adjuster**

- Memory controller can **adjust** DRAM internal DQS/DQ duty cycle

- Compensate for duty cycle error of all DQS/DQ

- Register-adjustable in 8-steps each, positive and negative

- 28 to 56 ps adjustment range

- Global or per-pin adjustment

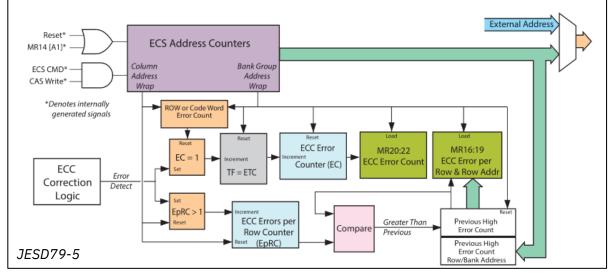

# **On-Die ECC**

- Single Error Correction

- 128 data bits, 8 ECC check bits

- Data to Memory Code Word to Memory Check Bit Check Bits Generator Check Bits Code Word No Error Syndrome Syndrome Syndrome Decode Generator from Memory Data from Memory CE Error Location Corrected Data Error Correctior JESD79-5

On-Die ECC Block Diagram

- DRAM **dynamically corrects** single-bit errors

- Error **counting**/tracking

ECC Transparency and Error Scrub Block Diagram

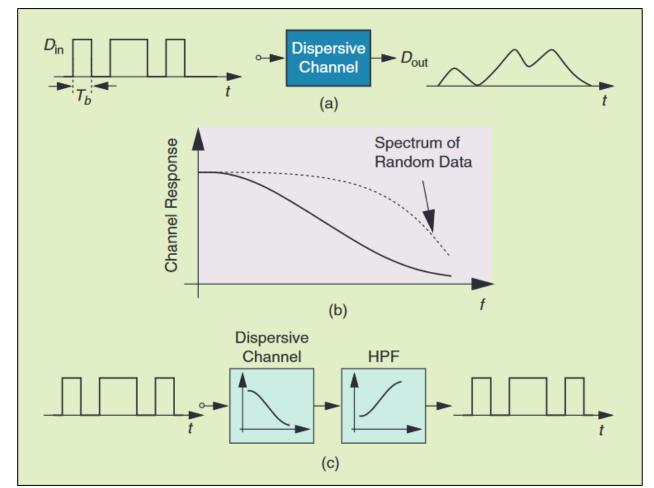

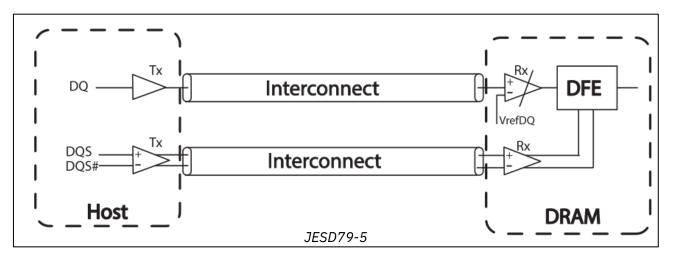

# **Decision Feedback Equalization**

- **ISI** increases and eye closes

- Due to higher data rates (at or above 3200 MT/s)

- Memory channels are **reflective**

- Due to many impedance discontinuities

- Provides a high frequency

**boost**

- Compensates for channel loss

From Razavi, "The Decision-Feedback Equalizer"

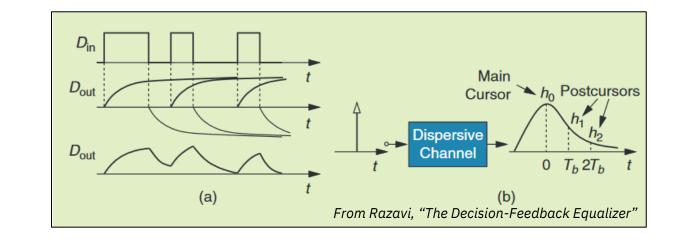

# **Decision Feedback Equalization**

- Approximate **linear equalization** with FIR filter

- Only **linear** stages (delay and scaling)

- Typical pros/cons of DFE

- No amplification of **noise** (such as CTLE)

- No pre-cursor equalization

- Remove **scaled interference** from four previous bits

- Based on the channel impulse response

- Four bits in a 4-tap DFE

# **Decision Feedback Equalization**

- **4-Tap DFE** equalizes DQ signals

- May implement 1-way, 2-way or 4-way interleaved DFE

- 1-way shown below

- Interleaving reduces slicer clock rate (and power) Taps 1-4

- Gain Bias:

- -6 dB to +6 dB

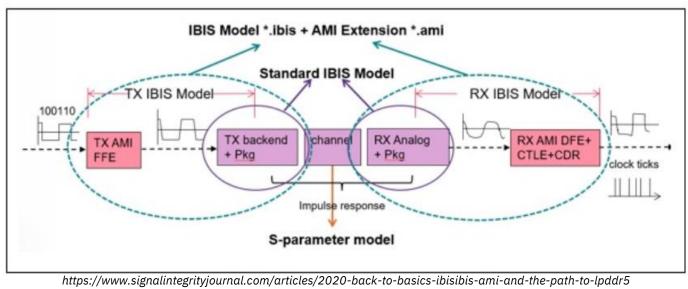

# **Bringing It All Together: Simulation**

- DDR5 made things better with DFE

- But with increased data rate, **simulation is a must** to ensure successful system design

- Questions arise:

- Advanced processing is on-chip with DFE, how do we simulate this?

- Is a vendor AMI model required?

- Will my power distribution network design withstand the faster switching speed?

- In order to answer the question: "How do you know it will work?"

- We will incorporate both IBIS-AMI and power-aware simulation

# **3. DDR5 Simulation**

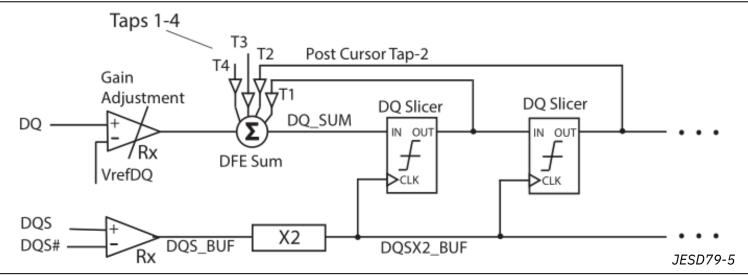

# What is IBIS-AMI?

- Algorithmic Modeling Interface

- Extends traditional IBIS (behavioral models)

- Equalization and other non-LTI effects

- Ultra-low BER (statistical simulation)

- Package sNp models

- Statistical simulation based on channel pulse response, or

- Time-domain simulation

### Demo: Plan

- Simulate one byte lane (DQ + DQS)

- 6400 MT/s

- 10" PCB trace model

- DFE on the receiver

- Verify minimum eye height/width meets spec (70mV/0.25UI at BER > 1E-16)

# **Demo: Setup and PCB**

- Prep: Have IBIS model in a clean directory ready to use

- Open TopXplorer, start a new topology

- Menu: Topology->New

- Create a SystemSI/Parallel Bus Analysis/Blank

- Add CTRL IBIS, MEM IBIS

- Add Trace Model

- Edit Trace, Microstrip:

- 10x, 4mil width, 4mil space, 0.7mil thickness, 4mil substrate

- System has extremely tight density requirements and cannot use up more area

- Length: 10000mil

- Include Power

- Edit VRM: Voltage range: 1.1 V Typical; 1.067 to 1.166 V

# **Demo: Controller IBIS**

- Load IBIS

- Select component "DDR5\_Controller"

- Check "Explicit IO Power/Ground Terminals"

- Verify the Bus Definitions

- Select CTRL IBIS

- Uncheck "Ideal Power"

- Check "Package Parasitics"

- Redo same steps for receiver (Don't forget to select receiver component)

# **Demo: Connections**

- Controller side:

- Verify power and grounds connected

- Select DQ0 to DQ7 and A-H, right click and "Connect by pin pair"

- Same with DQS0 P/N and I/J

- Follow same steps between trace and receiver

# **Demo: Simulation Setup**

- Check "Use Channel Simulator"

- Check Connectivity, verify magnitude is ~0.8

- Set timing budget

- Set data rate to 6.4 Gbps

- Set Analysis Options

- Corner Keep only Typ selected

- Bus Simulation select write only

- Channel Sim No change

- IO Models:

- Change stimulus to PRBS32

- Verify DQS still 01/10

- Change bits to display: Last 1000

- Change jitter to include both RJ and DJ

- Check only DQ0 and DQS P/N (Too long to run simulate all)

# **Demo: Simulate**

- Save Topology

- Enable Distributed and Set up Resources (Default)

- Run (Note: takes 2.5min on my machine)

Poll Question

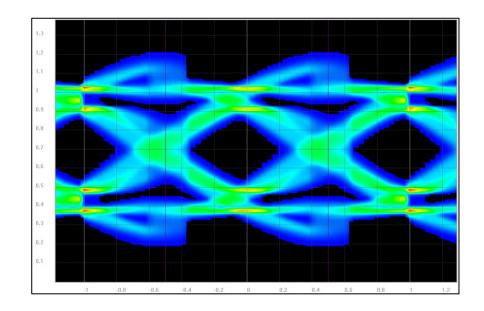

# **Demo: Simulate**

- Save Topology

- Enable Distributed and Set up Resources (Default)

- Run (Note: takes 2.5min on my machine)

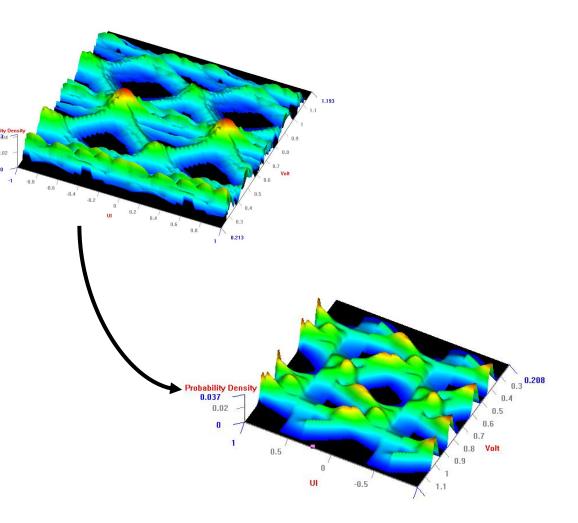

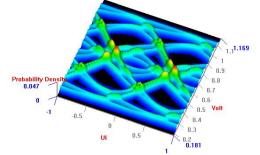

- Eye is closed

- NOTE: Mention that this configuration wouldn't have worked with DDR4, but with the new addition of DFE to DDR5 we can make it work at even higher data rates

# **Demo: Add DFE**

- Right-click the MEM IBIS and choose "Add AMI"

- Select the included "Memory Licensed" AMI/DLL files

- Review the DFE tap settings (4-tap for DDR5)

- Re-run

- Poll Question:

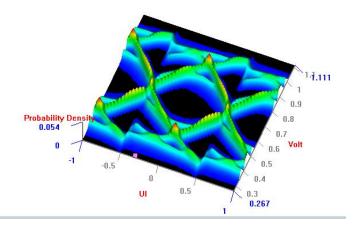

# **Demo: Add DFE**

- Right-click the MEM IBIS and choose "Add AMI"

- Select the included "Memory Licensed" AMI/DLL files

- Review the DFE tap settings (4-tap for DDR5)

- Re-run

- Results in a wide-open eye (0.54UI/140mV at BER of 1E-16)

- Meets our requirements

# Conclusion

- DDR5 is a **major** performance improvement

- Speeds from 3200 MT/s up to 8400 MT/s

- More **complex** simulation than DDR4

• Tools exist which can ensure **successful** design of your DDR5 system

### References

#### 1. JEDEC JESD 79-5, DDR5 Specification

- 1. <u>https://www.jedec.org/system/files/docs/JESD79-5.pdf</u>

- 2. JEDEC JESD 79-4, DDR4 Specification

- 1. https://www.jedec.org/system/files/docs/JESD79-4.pdf

- 3. JEDEC JESD 301-1 PMIC Specification

- 1. <u>https://www.jedec.org/system/files/docs/JESD301-1.pdf</u>

#### 4. Micron DDR5: Key Module Features

- 1. <u>https://media-www.micron.com/-/media/client/global/documents/products/technical-marketing-</u> <u>brief/ddr5\_key\_module\_features\_tech\_brief.pdf</u>

- 5. Razavi, The Decision-Feedback Equalizer

- 1. <u>https://www.seas.ucla.edu/brweb/papers/Journals/BRFall17DFE.pdf</u>

# Thank you!