DDR Signal Integrity Metrics Check Workshop

Learn how to analyze reflection and crosstalk for DDR signals using Sigrity with the DDR Signal Integrity Metrics Check Workshop.

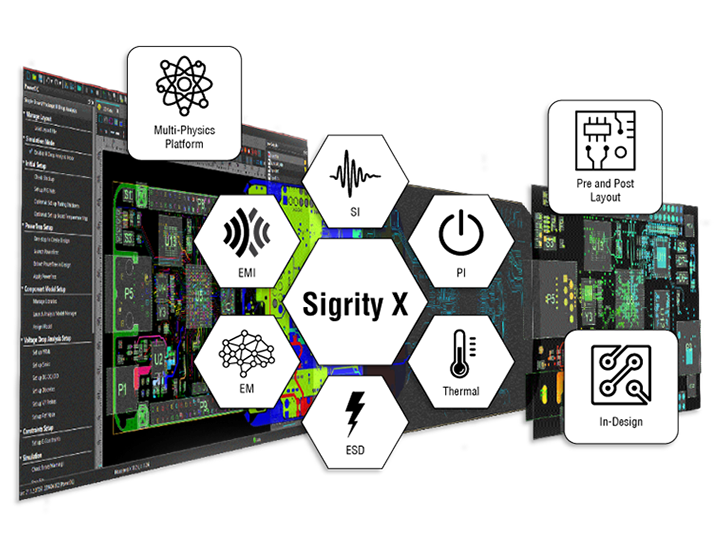

Complete electrical analysis platform built to help you solve all your SI, PI, and EMC design challenges across the board.

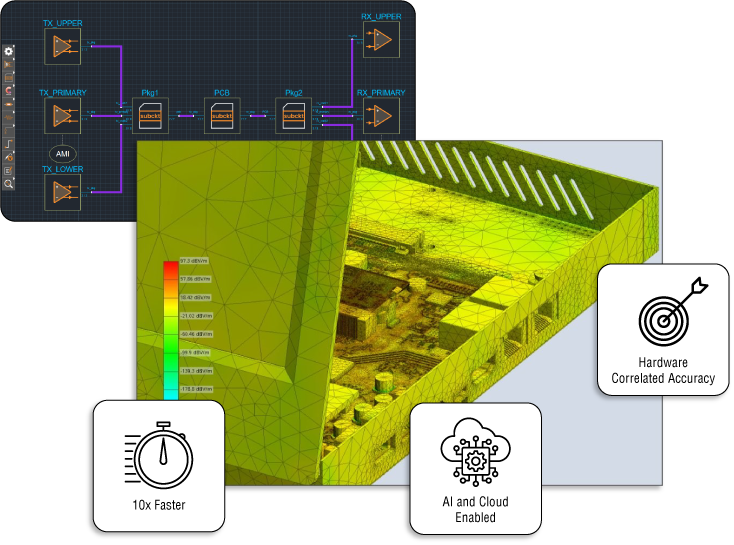

If you hope to stay ahead of the competition, you must determine optimal design configurations, validate performance, and signoff on your critical interconnects well before you get to prototype. Sigrity X provides the only complete analysis solution designed to solve today’s multi-physics, multi-domain design challenges.

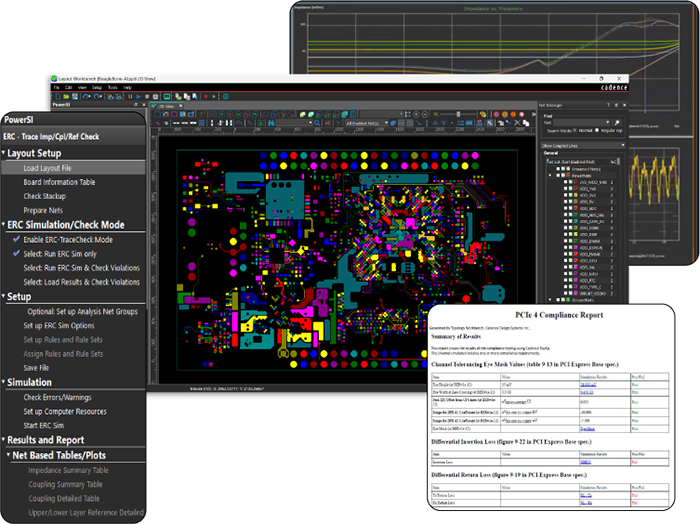

Sigrity allows you to move to production with confidence by providing a complete sign-off level design, analysis, and compliance environment for your critical serial link and parallel bus interfaces.

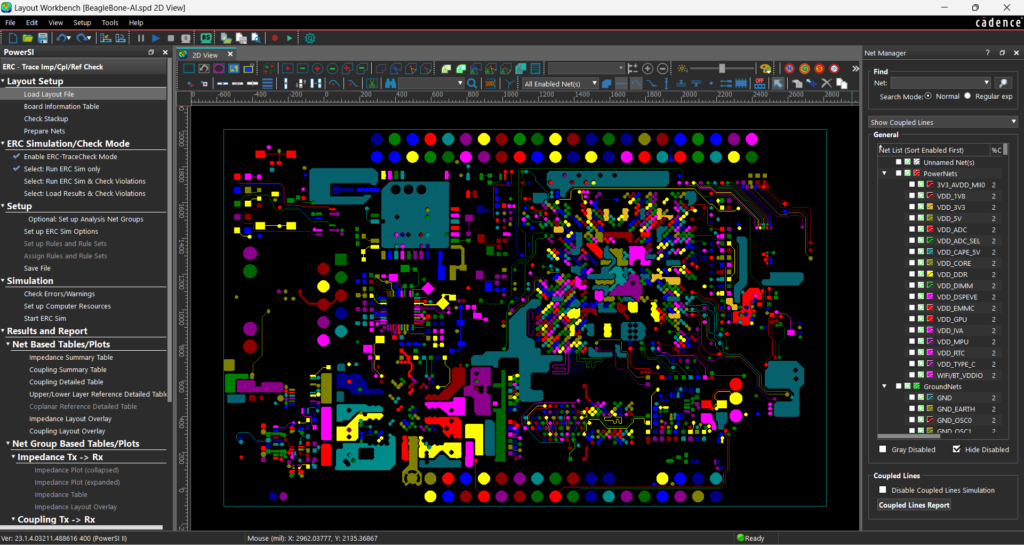

Achieve comprehensive electrical analysis of PCB and full IC packages with accurate, power-aware pre-layout and post-layout simulation to improve signal quality and performance.

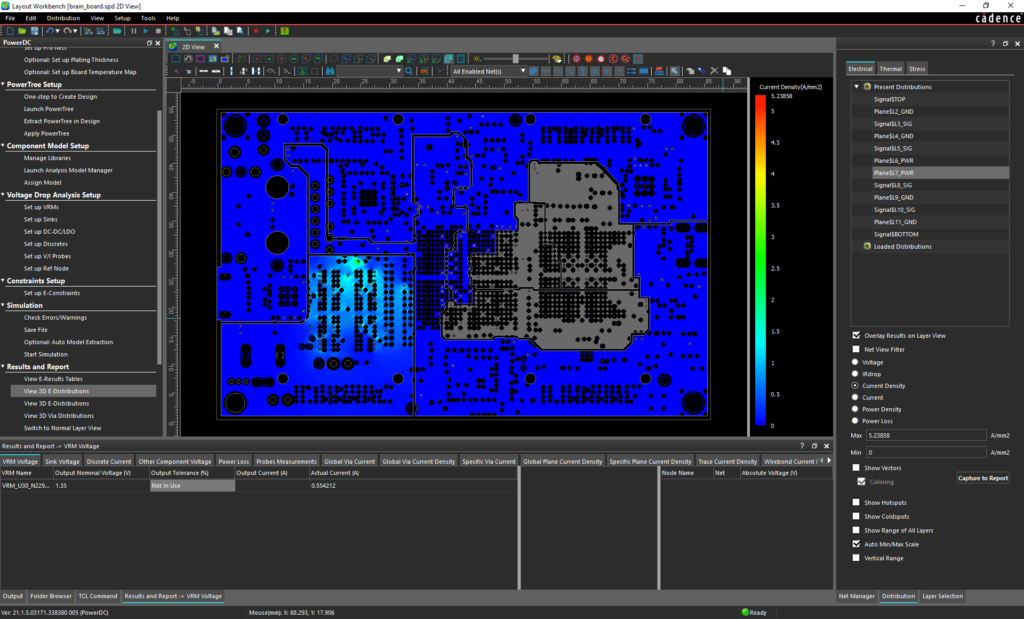

Analyze and optimize your Power Delivery Network (PDN) using AC frequency analysis as well as pre-layout and post-layout simulations to adhere to PDN requirements at the lowest possible cost.

Sigrity X EM analysis solutions are built for accuracy and speed enabling you to simulate your increasingly complex structures without compromise. With a 10x performance increase over the competition you can be assured you will be able to simulate with the fidelity you need and the speed you want. Multiple solver engines enable designers to leverage the best solver for the task (or deploy a combination) all from a cohesive and intuitive user interface.

Analyze near-field E/H densities and radiation effects as well as the impact of external radiation to easily identify problematic EMI radiating devices, determine necessary shielding and faraday cage placement, and evaluate overall system susceptibility.

Heat is one of the biggest factors in the performance, reliability, and safety of your PCB designs. Thermal effects can be simulated and heat mitigation efforts can be incorporated within your electronics early using Sigrity X. Efficiently identify hotspots and optimize your thermal profile as you design to ensure products will stay cool and function as intended.

Emulate and analyze the effects of a physical ESD gun on the design to prevent product damage, ensure adherence to regulatory standards and improve reliability.

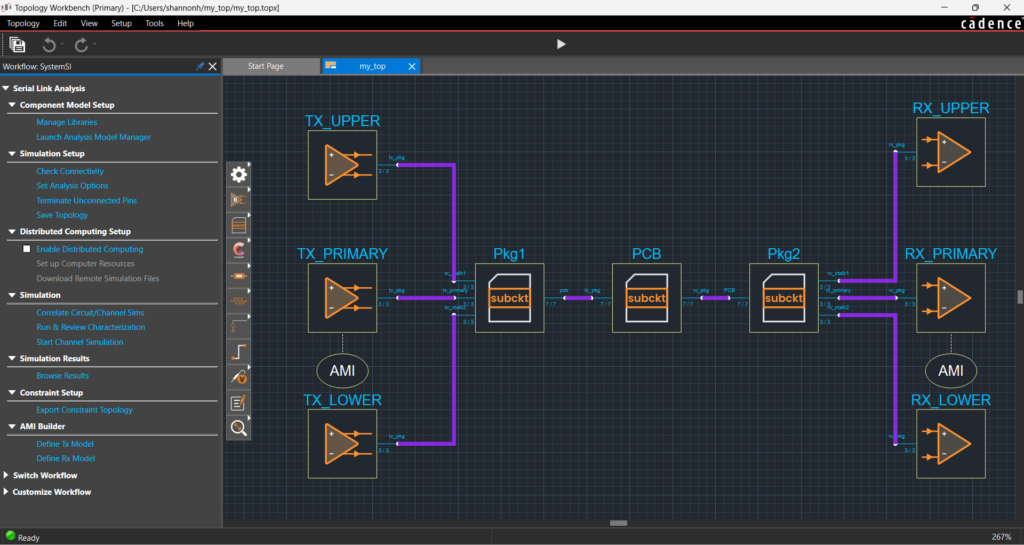

The unique, workflow-driven design environment and comprehensive simulation engines allow you to quickly access and perform the analysis needed to meet your design goals. As your analysis requirements increase, easily add additional workflows all within the same common UI. Never miss a step or feel unsure of your simulation setup with Sigrity workflow driven analysis.

The unique, workflow-driven design environment and comprehensive simulation engines allow you to quickly access and perform the analysis needed to meet your design goals. As your analysis requirements increase, easily add additional workflows all within the same common UI. Never miss a step or feel unsure of your simulation setup with Sigrity workflow driven analysis.

Perform comprehensive analysis of your PCBs regardless of the file format or CAD tool used for the design. Sigrity X accepts neutral file formats, such as IPC-2581 and ODB++, as well as CAD-specific files such as Altium, Cadence, Mentor, and Zuken.

Drastically reduce simulation setup time and errors with PCB & IC PKG aware setup with Sigrity X. Sigrity X understands PCB & Package structures and natively integrates with the Cadence PCB file formats to automate port configurations and make flex and rigid-flex simulation setup easy and straightforward.

Automatically generate reports containing tabular data, plots, pass/fail results, and more to efficiently communicate the analysis and required changes for your PCB designs.

Simulation shouldn’t be a singular event for the end of the design. To maximize the benefit and effectiveness of simulation in your design flow it is important to be able to simulate effectively at any stage. Sigrity X provides access to the most comprehensive range of simulation engines and tools to allow for full multi-physics analysis to occur at all phases enabling a true simulation driven digital twin-based design flow.

Gain access to the full Sigrity X platform on-demand with Sigrity tokens. Sigrity tokens solves one of the most prevalent problems for teams looking to adopt a simulation-driven workflow, usage and solver access. Traditional models require purchase of each solver and analysis tool separately with many of the tools sitting idle while those particular simulation engines are not needed. This makes justifying the cost of simulation tools a big challenge and leaves you susceptible to other SI/PI issues that cannot be analyzed. Sigrity tokens allows teams to leverage the full Sigrity X portfolio on-demand saving significant costs and enabling simulation to be broadly used throughout the design process, ensuring high utilization and efficiency.

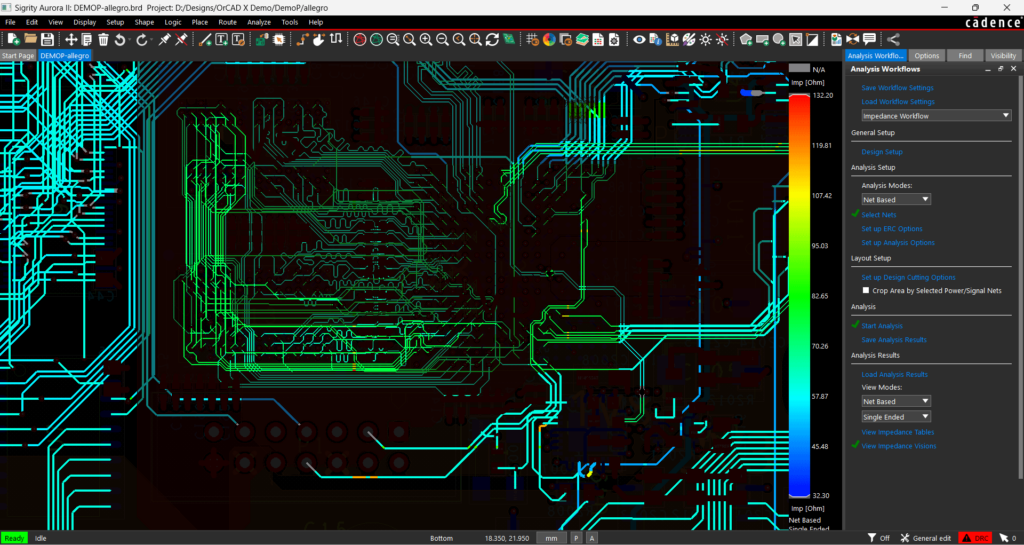

Analyze common SI and PI problems without leaving your PCB design environment. Graphical overlays as well as tabular results help you easily identify and correct issues directly in the PCB canvas as you design.

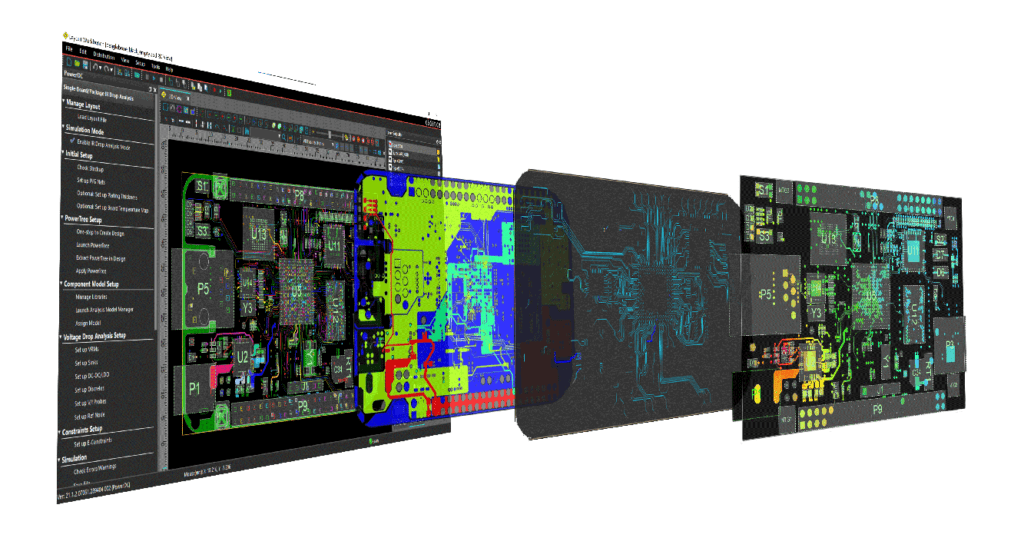

TopXP provides a ready-made interface for pre and post layout exploration and analysis. From single board to multi-board system level simulation, TopXP provides the flexible easy-to-use environment needed to perform your SI/PI analysis.

Interact with the physical design and run full board simulation and extraction to build models and test your design effectiveness. Perform multi-corner optimization, such as decap placement, with ease.

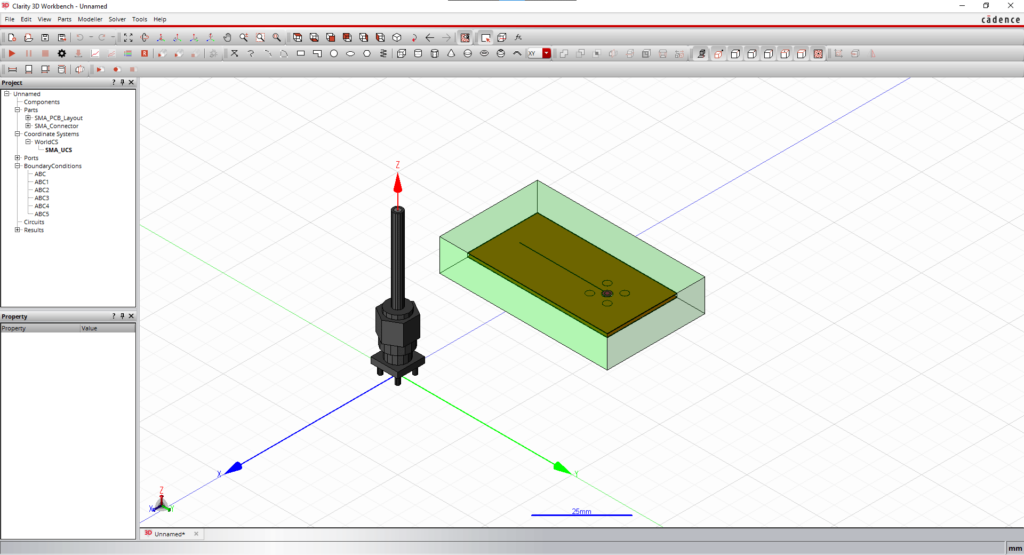

Easily and model your complex 3D structures from via, to connectors, and full flex PCBs. With automated setup and unmatched performance, you can ensure hardware correlated accuracy for your critical 3D structures.

Often the size and granularity of simulations required to obtain a real-world analysis results in lengthy run times that are not feasible in today’s fast-paced markets. Sigrity X allows you to build true virtual prototypes and perform analysis quickly with the industry leading performance, capacity, and accuracy.

Full multi-threading support allows you to accelerate analysis speed even farther by leveraging your multi-core compute resources to go from run to results in no-time.

Easily leverage the cloud to scale your compute resources with near linear improvement in performance. With the lowest memory footprint on the market, you can scale cost effectively levering less expensive compute resources while producing faster results.

Clarity 3D EM was architected from the ground up and provides the fastest, highest capacity, lowest memory footprint solution for EM extraction. Simulate with confidence knowing that you can handle the most complex solution spaces without approximation or cut and stitch, ensuring what you analyze represents what you will build.

Analyze and verify with confidence knowing your results will have tight correlation to real-world hardware. Cadence rigorously tests Sigrity X against their own hardware ensuring the correlation you need to sign-off with confidence.

AI-powered optimization architecture enables efficient evaluation of design corners and design alternatives to perform hardware-accurate system-level optimization in a fraction of the time based on defined design goals.

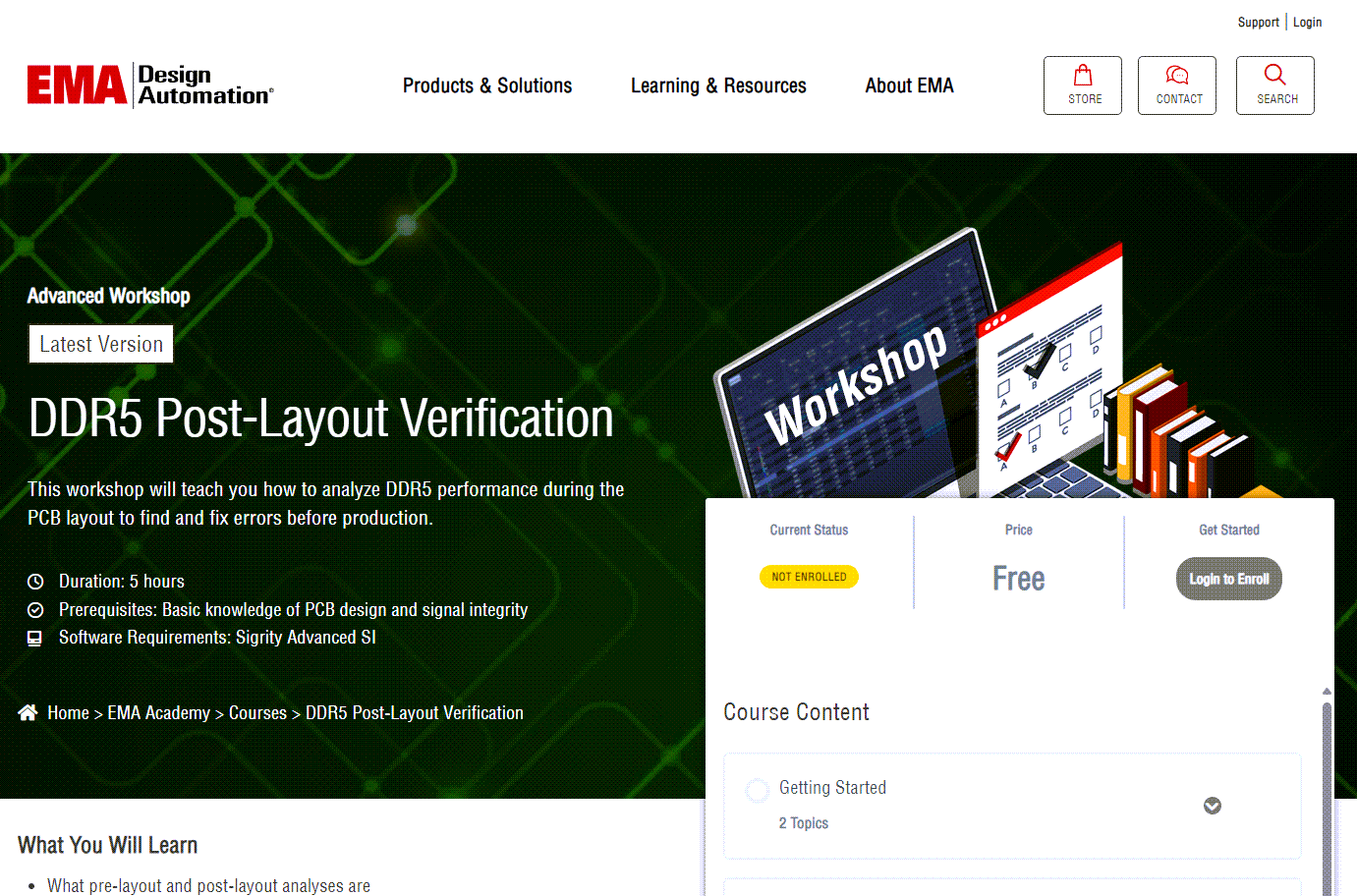

Access free training materials from EMA and Cadence to get you simulating with maximum efficiency right from the start.

From single users to large teams Sigrity X enables you to leverage simulation at all phases.

Get access to the easy-to-use comprehensive simulation environment which allows you to run analysis quickly and accurately across SI, PI, Thermal and more.

Sigrity provides the fastest, highest capacity simulation environment available. Expert level users need expert level tools that can support the complex design challenges you are faced with. Sigrity represents the most advanced electronics multi-physics simulation platform available on the market.

Sigrity X provides integrated in-design analysis allowing you to run simulations as you design. Save time, prevent errors, and leverage simulation to improve your design efficiency with the first simulation environment built to work inside the existing PCB design flow.

Future proof your design team with access to the leading multi-physics analysis platform on the market. Enable your team with the tools they need to identify and solve any electrical analysis issue upfront through simulation. The unique Sigrity X token-based licensing model provides easy access to all the simulation tools and allows you to effectively bring simulation to all users without heavy licenses and access costs. Bring your design predictability, performance, and accuracy to new heights with Sigrity X.

Over 30 years’ experience helping engineers design, validate, and build hardware successfully.

Learn how to leverage all the functionality Sigrity X has to offer.

Learn how to analyze reflection and crosstalk for DDR signals using Sigrity with the DDR Signal Integrity Metrics Check Workshop.