Modern electronics could not exist without semiconductors and digital electronics but as electronics become faster and more complex, it’s essential to model realistic behavior to ensure design accuracy. At high speeds, digital electronics are susceptible to issues with propagation delay, and any stray capacitance present on the board could lead to attenuation, which could prevent a high input from ever reaching the device’s threshold voltage. PSpice allows you to quickly create a custom SR latch SPICE model for accurate simulation of digital designs with a wizard-based approach.

This quick how-to will provide step-by-step instructions on how to create a create a SR latch SPICE model in PSpice with the Modeling Application.

To follow along, download the materials provided above the table of contents.

How-To Video

Open in New Window

Open in New Window

Create an SR Latch SPICE Model

Step 1: Open the provided design in PSpice 23.1.

Note: A wizard-based approach to digital models is new in version 23.1. See other new features here.

Step 2: Select Place > PSpice Part > Modeling Application from the menu.

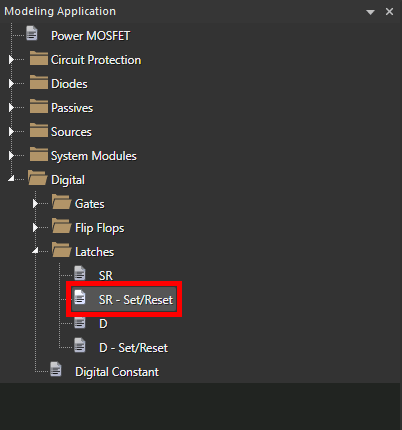

Step 3: In the Modeling Application, expand Digital > Latches.

Step 4: Select SR – Set/Reset. This model contains PRESET and CLEAR pins, which can be used to set and override the output of the latch.

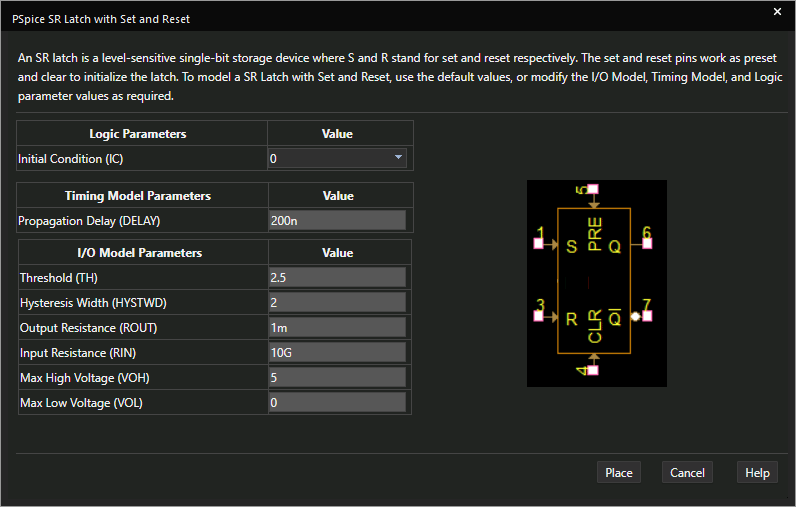

Step 5: The SR Latch options window opens. Enter the following model parameters:

- Initial Condition: 0

- Propagation Delay: 200n

- Threshold: 2.5

- Hysteresis Width: 2

- Output Resistance: 1m

- Input Resistance: 10G

Note: The logic device being modeled has negligible output resistance and requires negligible input current. Learn how to identify these parameters from device datasheets to create a realistic representation of SR latches here.

Step 6: Click Place.

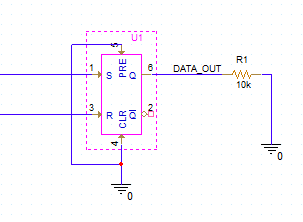

Step 7: Click to place the latch in the schematic.

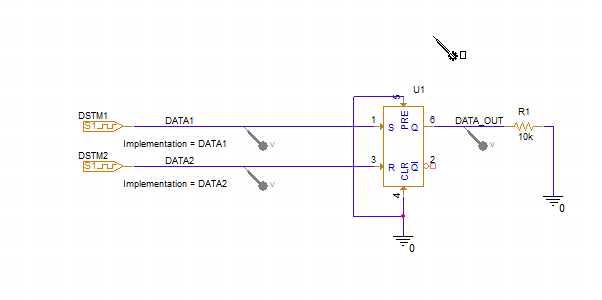

Step 8: Select the Voltage/Level Marker button from the toolbar.

Step 9: Click to place probes on the DATA1, DATA2, and DATA_OUT nets. Right-click and select End Mode when finished.

Running the Simulation

Step 10: Select PSpice > Run from the menu.

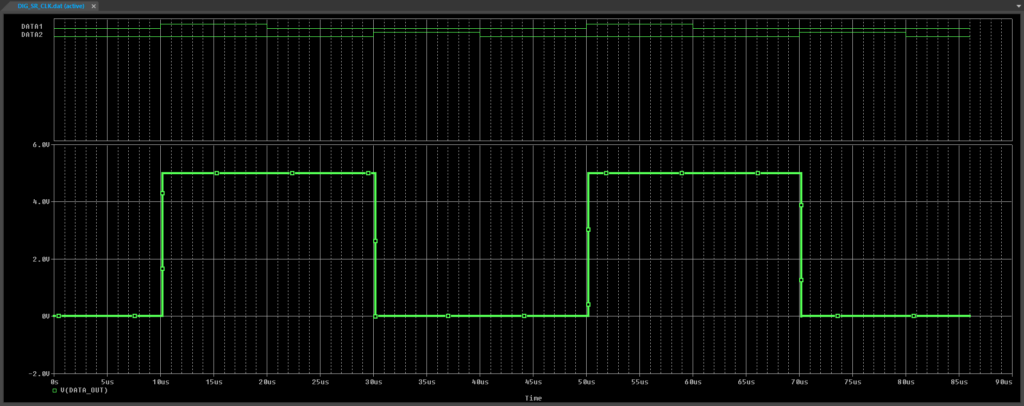

Step 11: View the simulation results. The output latches high when DATA1 is high and low when DATA2 is high.

Modifying the SR Latch SPICE Model

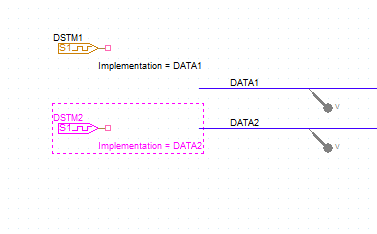

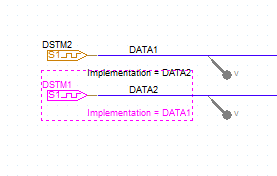

Step 12: Close the result window. Back in the schematic, hold Alt on your keyboard and click and drag stimulus DSTM1 away from the design.

Note: Holding Alt will disconnect the component from any wires.

Step 13: Hold Alt and click and drag stimulus DSTM2 away from the design.

Step 14: Click and drag to connect DSTM2 to the DATA1 net. Click and drag to connect DSTM1 to the DATA2 net.

Step 15: Select PSpice > Run from the menu.

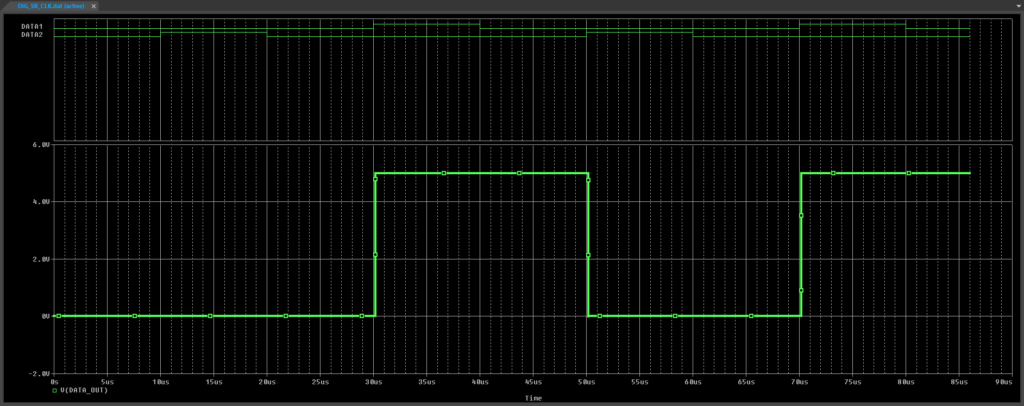

Step 16: View the results. The output pulses are now shifted.

Wrap Up & Next Steps

Quickly create the required SR Latch SPICE models and simulate accurate digital circuit behavior with the PSpice Modeling Application in PSpice. Upgrade to the latest 23.1 release or test out this feature and more with a free trial of OrCAD.