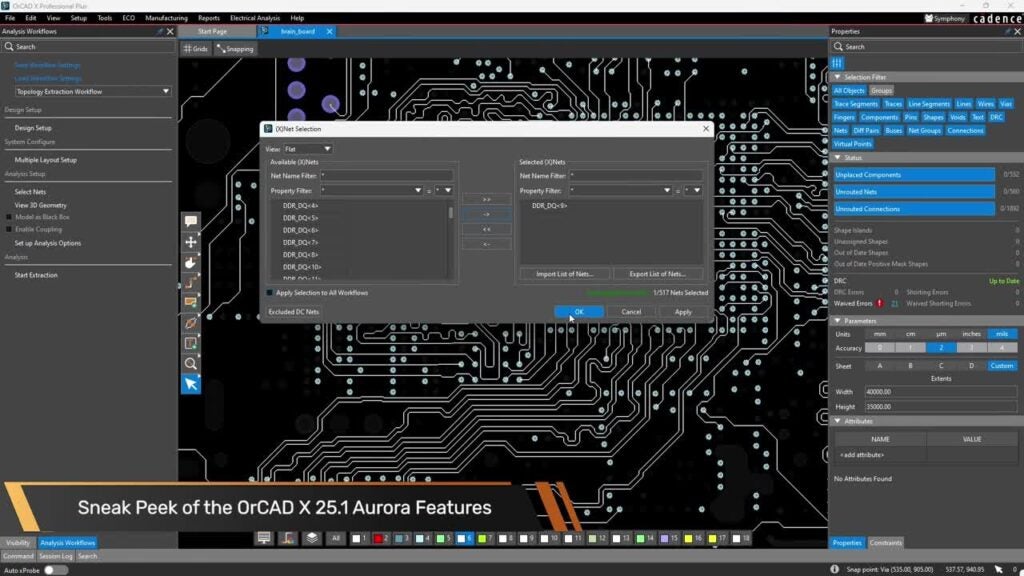

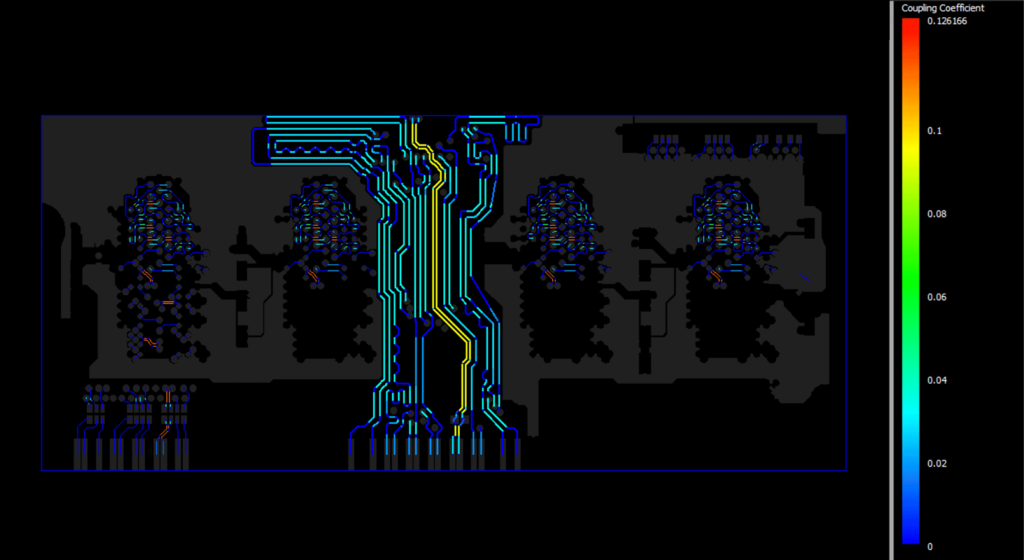

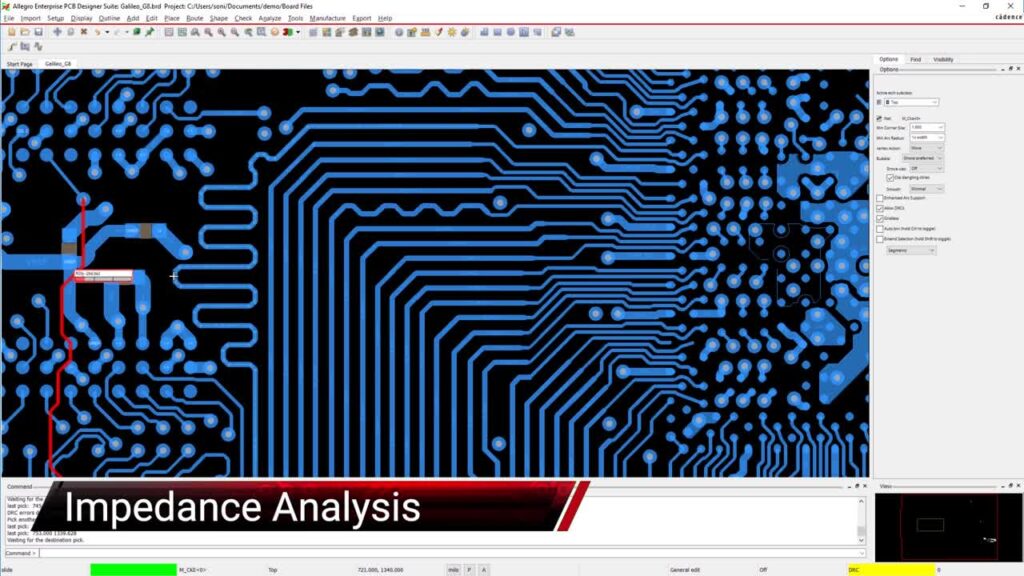

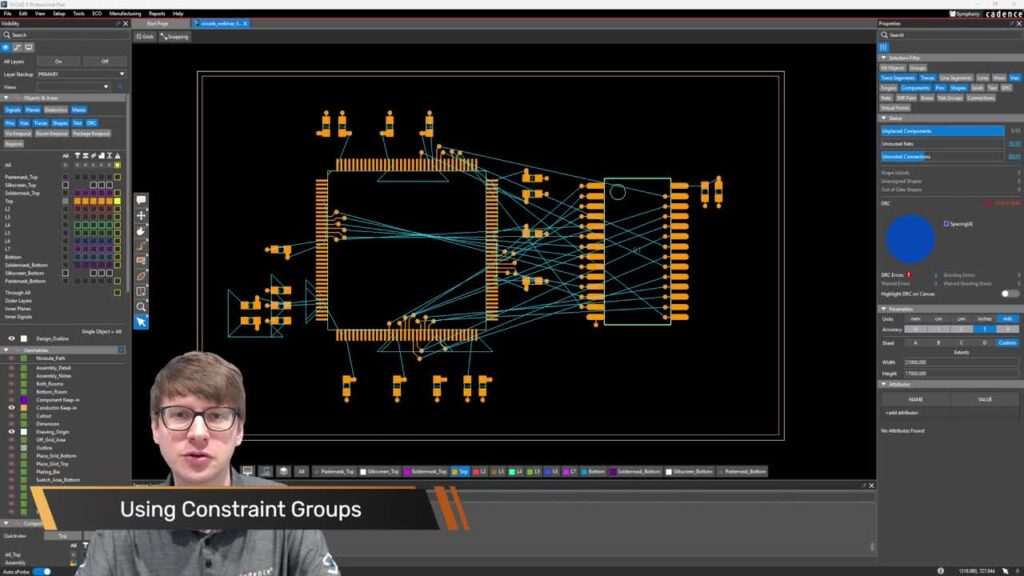

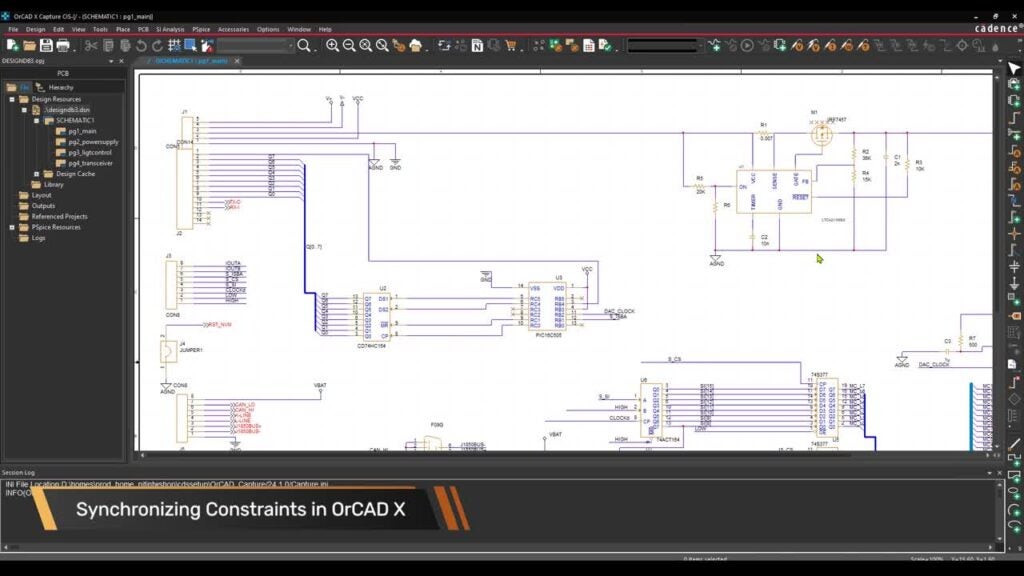

Sigrity Aurora enables signal and power integrity analysis in the familiar OrCAD and Allegro design environment to achieve an analysis-driven PCB design flow. In this video, we will add electrical constraints within a topology and implement the constraints for parallel data bus lanes. We will also update and audit the constraint manager to validate changes.

In this video, you will learn:

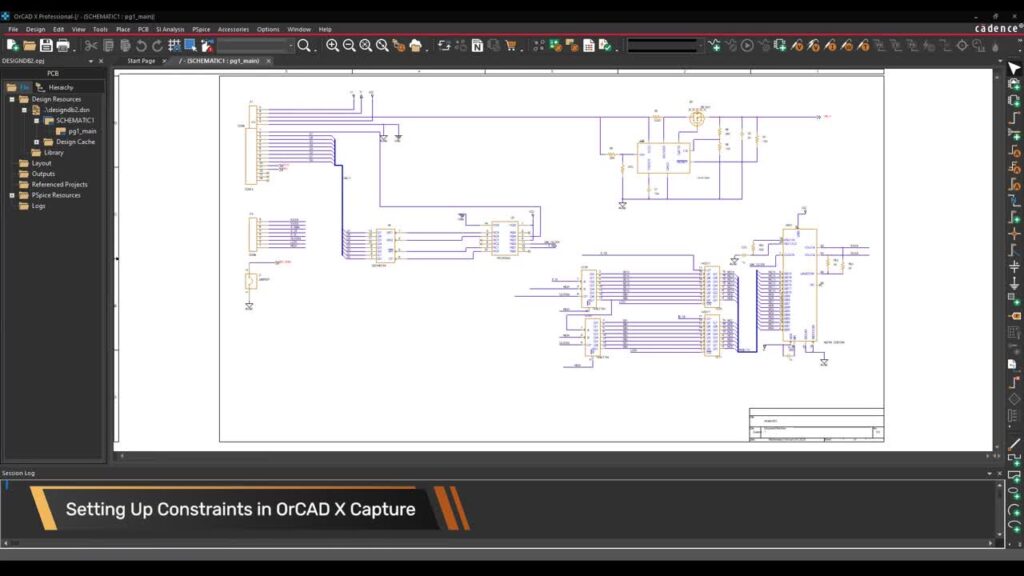

- How to add electrical constraints

- How to create electrical constraint sets (EC-Sets)

- How to apply electrical constraint sets

- How to audit the electrical constraint sets

- How to save the board file

Follow along with these demo files here.

For part 2 of this video series, click here.

For step-by-step instructions on how to use the workflows included in Sigrity Aurora, view our free workshops at EMA Academy.