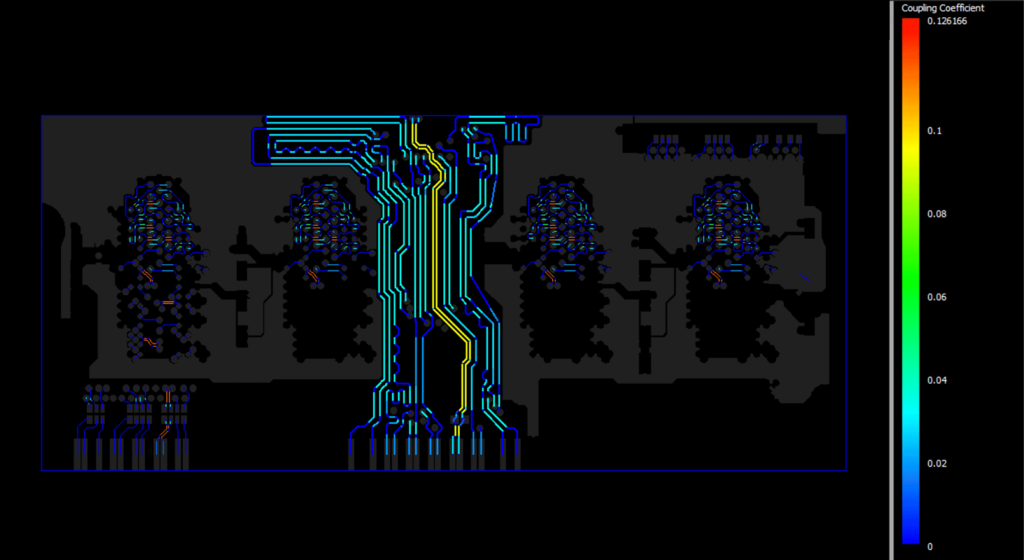

For an accurate analysis of DDR4, it is very important to incorporate the Power Delivery Network into the simulation and analyze the effect of noise due to switching of the parallel bus signal groups.

In this series of videos, we’ll learn how to model, simulate, and analyze a Power-Aware Parallel Bus System with Sigrity. In part 4 of this video series, we will teach you how to:

- Setup timing budget parameters

- Configure Simulation Analysis options

- Configure On die package parasitics for the controller and Memory

Follow along with these demo files: https://www.ema-eda.com/wp-content/uploads/2023/05/2023PAPBS_Part4.zip

This is part 4 of this video series:

- Modeling and Simulating a Power-Aware Parallel Bus System: Part 1

- Modeling and Simulating a Power-Aware Parallel Bus System: Part 2

- Modeling and Simulating a Power-Aware Parallel Bus System: Part 3

- Setting Analysis Options and Timing Budget for a Power-Aware Parallel Bus System

- Circuit Simulation and Analysis of a Power-Aware Parallel Bus System

Learn how to model a simple parallel bus system here.