Migrating from Altium Designer to Cadence Allegro X is more than just swapping software. While Altium excels in a unified, user-centric environment perfect for rapid prototyping and mid-complexity boards, Allegro is the industry standard for high-speed, constraint-driven enterprise design.

For teams scaling up to handle massive ball-grid arrays (BGAs), DDR5 routing, or multi-board systems, this transition is often inevitable. However, the move from a query-based rule system to a spreadsheet-based Constraint Manager can be jarring. This guide offers a technical, step-by-step pathway to migrate from Altium to Allegro so your designs, libraries, and workflows don’t lose data integrity.

When and Why to Migrate from Altium to Allegro?

The decision to migrate from Altium to Allegro typically triggers when a design team outgrows the “project-centric” model and requires a “data-centric” approach.

- Team Scalability: Allegro’s Symphony Team Design enables multiple designers to route the same board simultaneously in real time. If your team is deadlocked waiting for one person to release a file, it’s time to move.

- Complexity & High-Speed Constraints: Altium’s design rules are powerful but can become unwieldy for interfaces with hundreds of matched-length signals. Allegro’s Constraint Manager (CM) handles hierarchical rules (Electrical Constraint Sets) for propagation delay, phase tuning, and impedance with greater rigor.

- Ecosystem Integration: Large enterprises often require deep integration with SI/PI tools, such as Sigrity, and IC packaging tools. Allegro’s native file formats (.brd, .mcm) make these handoffs easy.

Feature Mapping Table

| Feature | Altium Designer | Cadence Allegro |

| File Extension | .PcbDoc (Binary) | .brd (Binary) |

| Library Format | .PcbLib and .IntLib (Unified) | .pad (Padstack), .dra (Drawing), .psm (Symbol) |

| Rule System | Query-Based (SQL-like) | Spreadsheet-Based (Constraint Manager) |

| Design Reuse | Snippets / Device Sheets | Replicate / Modules |

| Keepouts | Layer-specific Keepout Objects | Route Keepout / Via Keepout (Shape-based) |

Pre-Migration Checklist

Allegro has built-in translators to convert third-party design data into physical designs. However, before you touch a translator, sanitize your source data. Garbage in, garbage out is the cardinal rule of data migration.

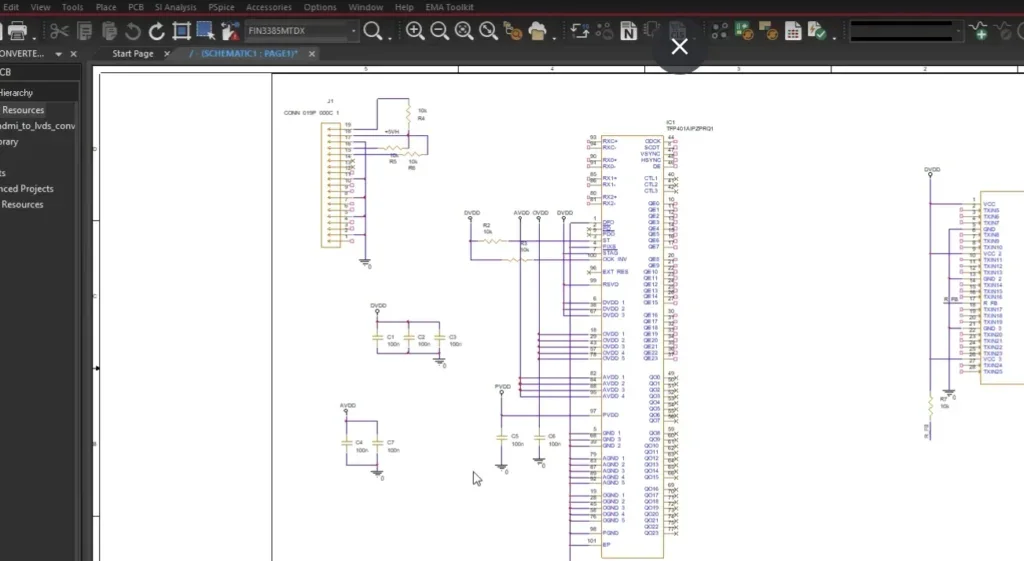

- Flatten Hierarchies: While Allegro supports hierarchy, deeply nested sheets in Altium can sometimes cause netlist mismatches during the schematic import (OrCAD Capture). Simplify where possible.

- Export Design Rules: You cannot directly import Altium rules into Allegro. Manually document your critical clearance, width, and high-speed rules in a spreadsheet. You will need to rebuild these in Allegro’s CM.

- Library Cleanup: Ensure all components in Altium have unique Design Item IDs. Duplicate IDs can cause the Allegro translator to overwrite symbol definitions, leading to incorrect footprints.

Data Transfer Methods

Converting the PCB Layout

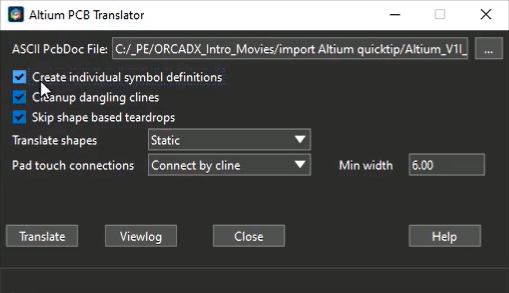

Direct binary import (.PcbDoc to .brd) is rarely supported natively without an intermediate ASCII step.

- Save as ASCII: In Altium, open your PCB and select File > Save As. Choose PCB ASCII File (*.PcbDoc). The standard binary format will not be readable by the Allegro translator.

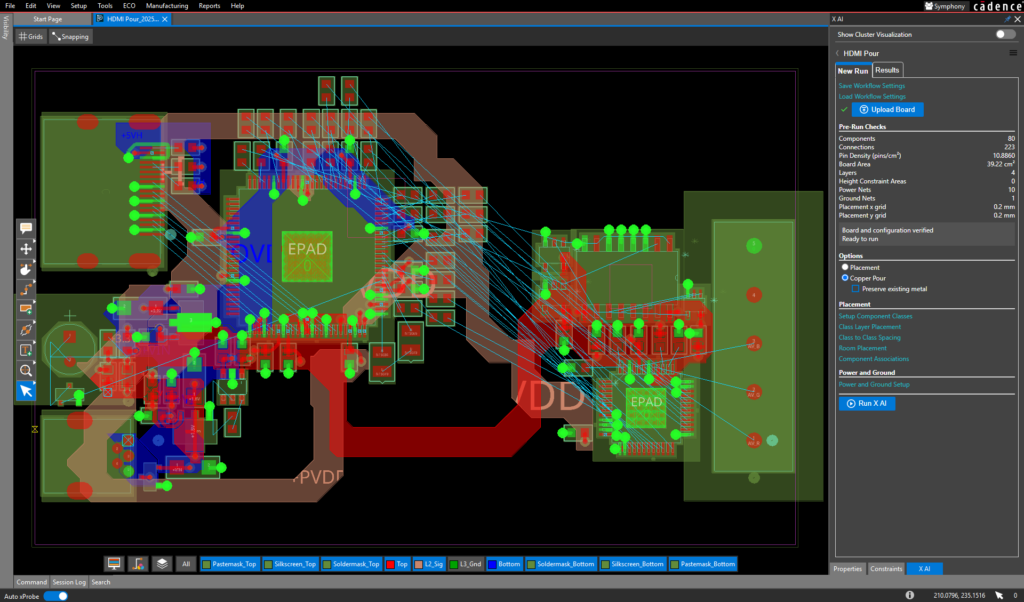

- Import in Allegro:

- Launch Allegro PCB Editor.

- Navigate to File > Import > CAD Translators > Altium PCB.

- Select your ASCII file.

Library Extraction

One advantage of the translation process is that it automatically separates the Altium design into Allegro library files.

- Padstacks (.pad): Generated for every unique pad style.

- Symbols (.psm): The physical footprint files.

- Drawings (.dra): The editable source for the symbols.

Rebuilding Workflows in Allegro

Once the geometry is in, the engineering work begins. The geometry needs to become data.

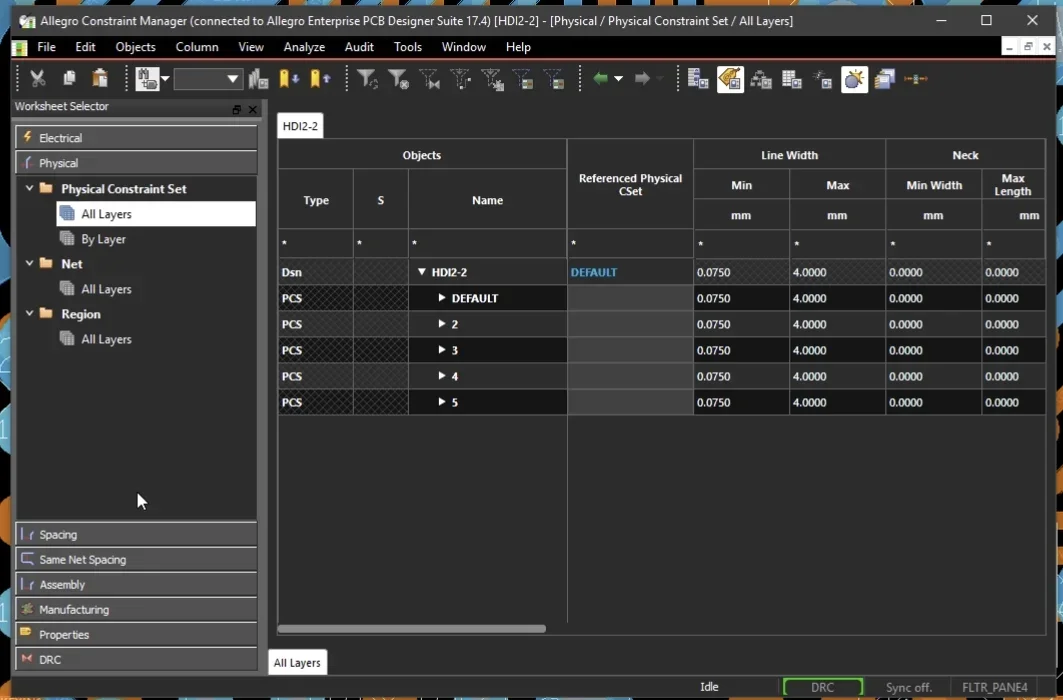

Constraints vs. Rules

In Altium, you might write a query: InNetClass(‘DDR’) AND IsTrack.

In Allegro, you’ll think in Sets.

- Open Setup > Constraints > Constraint Manager.

- Create a Physical Constraint Set for trace widths.

- Create a Spacing Constraint Set for clearances (Line-to-Line, Line-to-Pad).

- Assign these sets to your Net Groups (Buses).

Design Rule Check (DRC)

After import, your board will light up with DRC markers. This is normal.

- Update Shapes: Run Shape > Global Dynamic Params and trigger an update. This forces Allegro to recalculate voids around pads.

- Waive False Positives: You may see “Line to Line” errors where Altium allowed merging. Manually inspect and waive these or trim the artifacts.

SKILL Scripting

SKILL (Structured Knowledge Interchange Language) is a scripting language developed by Cadence and built into Allegro and other Cadence EDA tools. SKILL is used to automate PCB layout tasks, inspect and modify database objects, and efficiently resolve repetitive issues. Basic SKILL scripting is useful here.

- Text Scaling: Altium and Allegro render fonts differently. Imported text is often too large. Use a simple SKILL script to iterate through refdes (reference designator) labels and set a fixed text block size (e.g., width 20, height 25).

- Layer Cleanup: Use scripts to delete artifacts at coordinate (0,0), a common “dumping ground” for translation errors.

Validation: The Final Hurdles

Make sure to validate the design before ordering a spin.

1. Netlist Compare

This may be the most important step.

- Export an IPC-D-356 netlist from your original Altium project.

- Export an IPC-D-356 netlist from the new Allegro .brd file.

- Use a text editor or a CAM tool (like CAM350 or GerbTool) to diff the files. If the connectivity doesn’t match 100%, do not proceed.

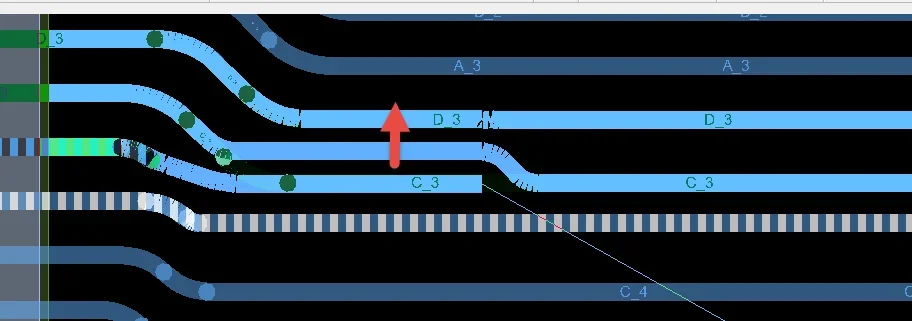

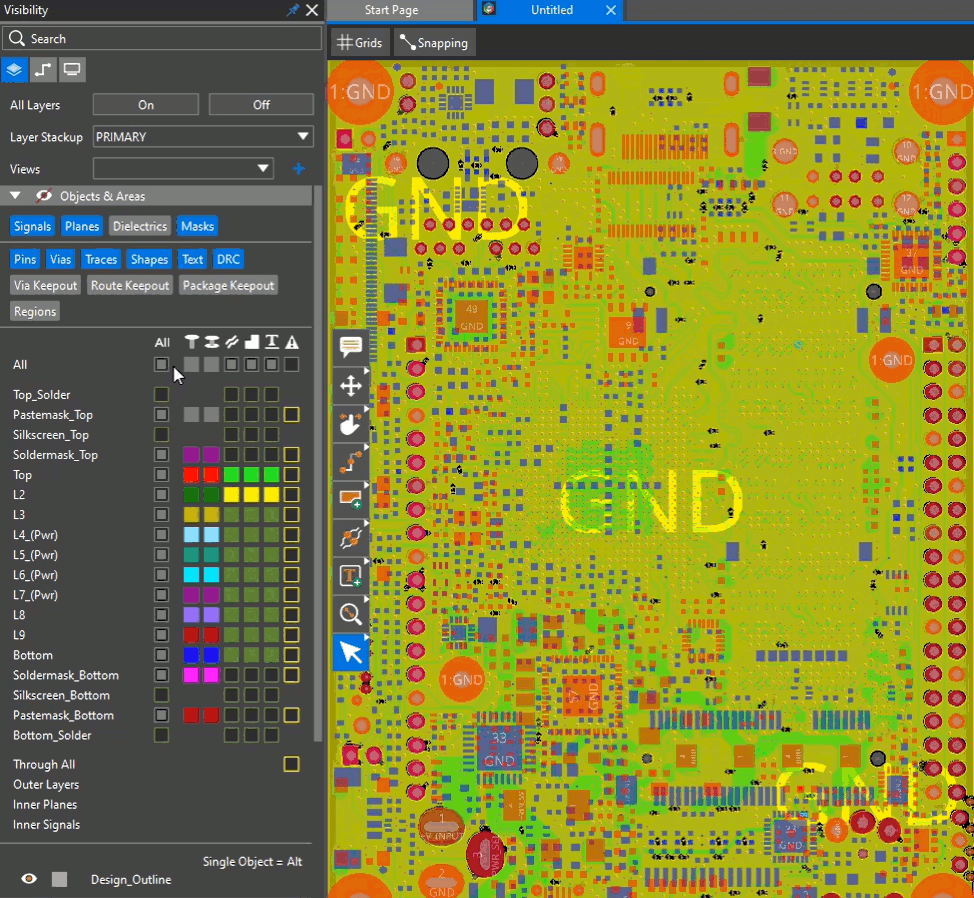

2. Visual Plane Check

Toggle the visibility of your plane layers. In Altium, negative planes are common. In Allegro, positive dynamic shapes are preferred for modern HDI designs. Ensure your thermal reliefs were generated correctly.

3. Design Review

Hold a “migration review” with your team. Walk through the Constraint Manager specifically. The most common failure mode in migration isn’t a short circuit; it’s a high-speed rule (like a differential pair gap) that got reset to default.

Migrating to Allegro may seem like a tall task, but it pays dividends in control and scalability. By respecting the differences in data structure and validating your constraints, you turn a painful transition into a strategic upgrade for your team.

EMA Design Automation is a leading provider of the resources that engineers rely on to accelerate innovation. We provide solutions that include PCB design and analysis packages, custom integration software, engineering expertise, and a comprehensive academy of learning and training materials, which enable you to create more efficiently.

For more information on how to migrate from Altium to Allegro and how we can help you or your team innovate faster, contact us.