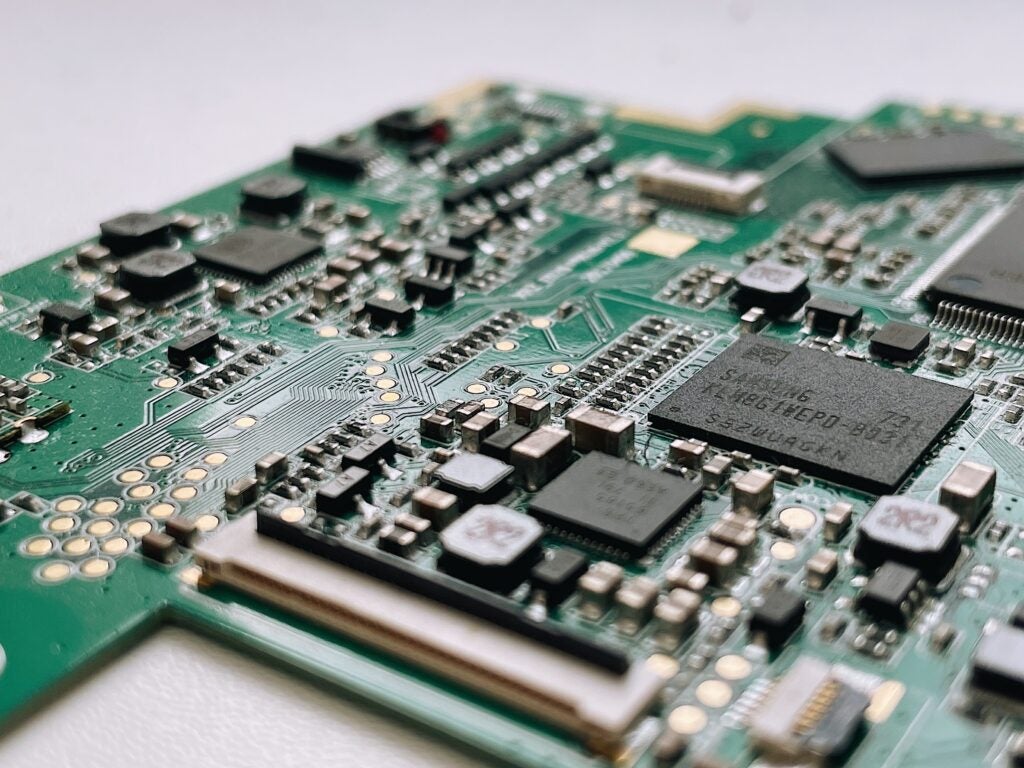

When engineers discuss signal integrity, the conversation generally revolves around high-speed circuit design. This is well-deserved as it is critical to know how to address the causes of reflection, impedance discontinuities and mismatch, and other issues for high-speed signal propagation. It is also important to remember that not all signals on your board are high-speed, yet signal quality is always a concern.

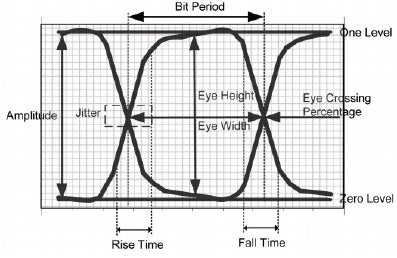

For example, every circuit board has grounding/return signals, and most boards include some type of interface–component to component, component to trace, trace to connector, etc.–where eye diagrams are invaluable in evaluating signal integrity. Therefore, understanding the best practices for PCB signal integrity simulation for various signal types is essential.

Signal Type and Simulation Needs

In order to ensure signal quality through your circuit board, it is important to know how to analyze the various signals that may be present such as those listed in the table below.

| PCB Signal Integrity Simulation Best Practices | |

| Signal Type | Simulation Best Practices |

| High-speed RF Signals | Model trace paths as transmission lines and analyze causes of crosstalk, reflections, and coupling. |

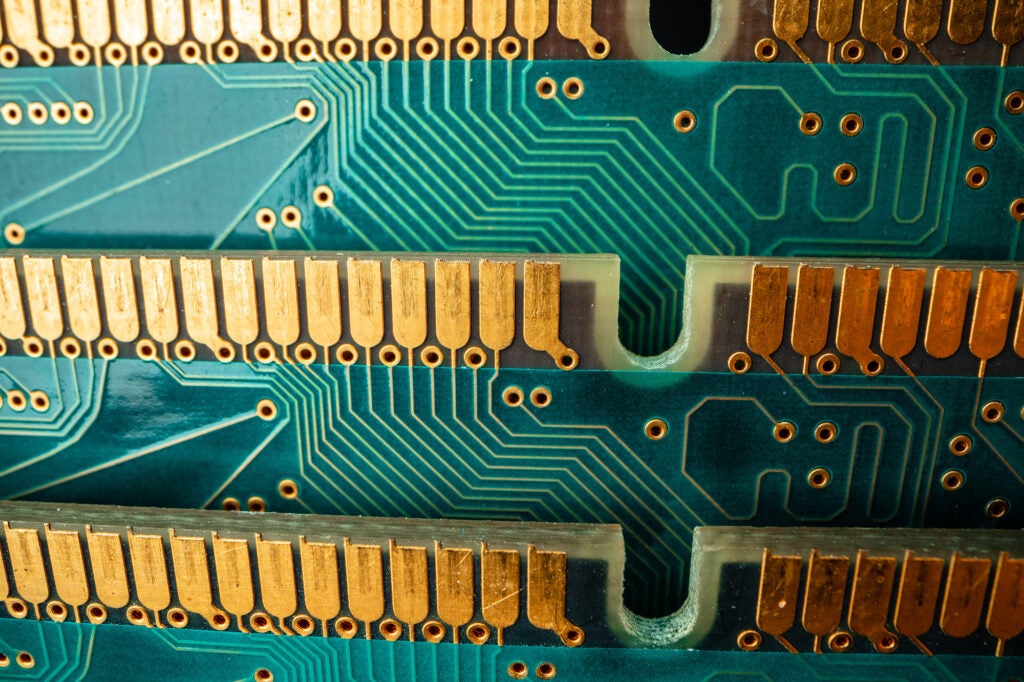

| Differential Signals | Differential pairs are commonly used for applications such as HDI signal transfer. Ensure trace pairs are equally spaced, and have identical copper weights and matching impedances. |

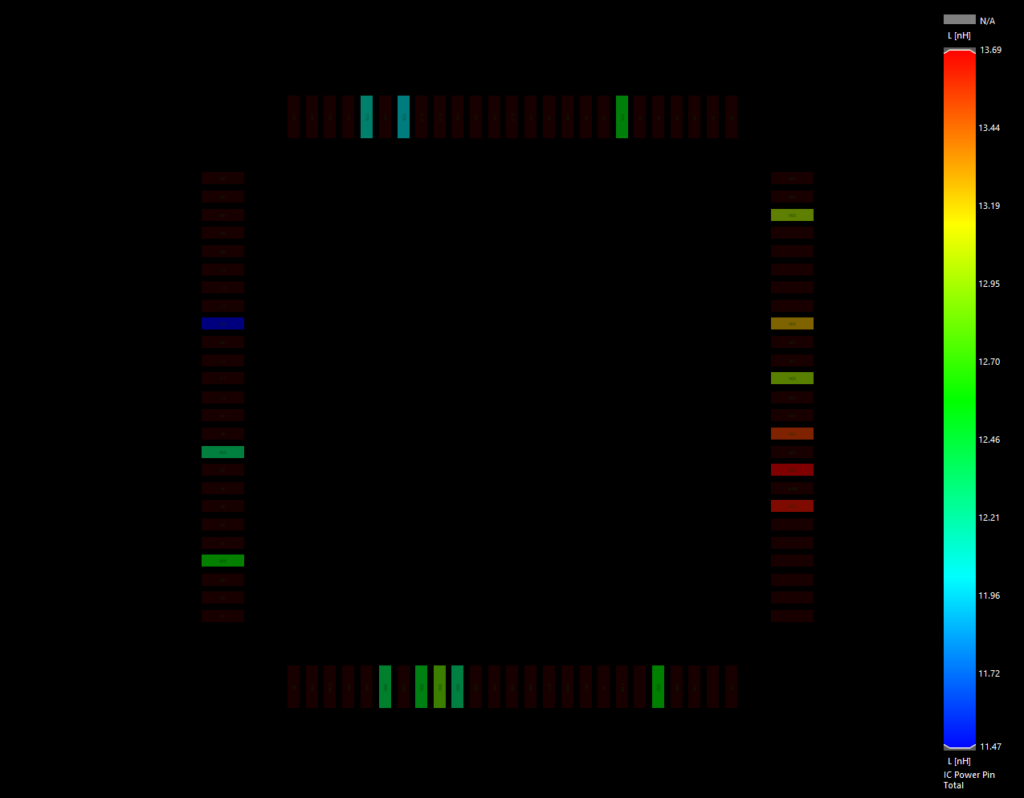

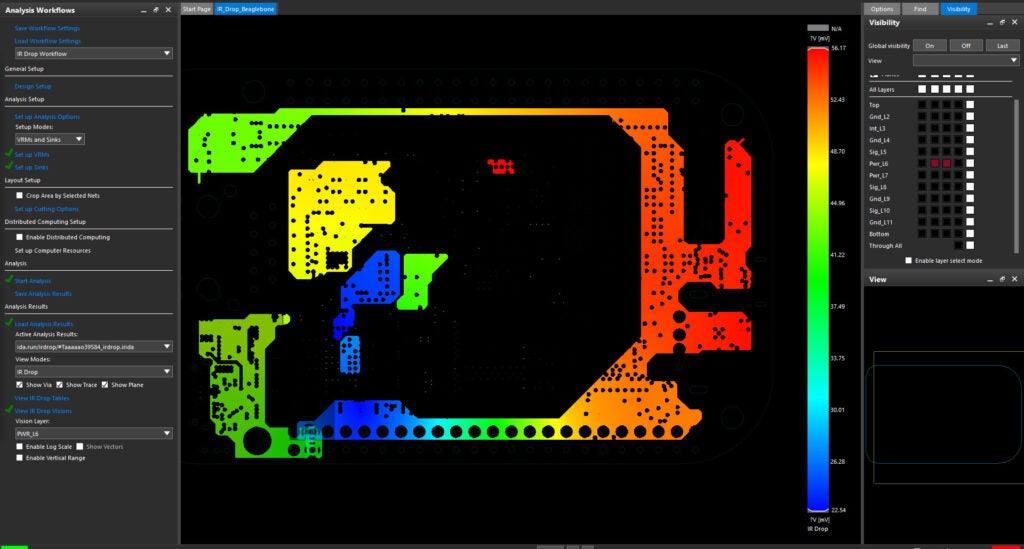

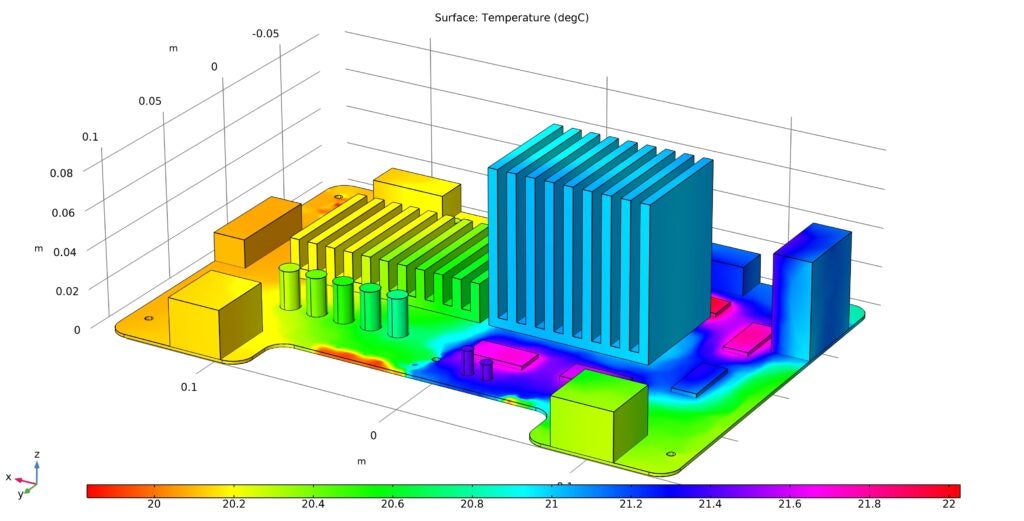

| Power Signals | Adequate power distribution to components and loads is imperative and must be analyzed and verified for analog and digital circuits. |

| Ground Signals and Returns | Evaluate path lengths, via placement, coupling effects, and any ground bounce due to switching transitions. |

| Timing Signals | Clock signals require analysis of skew, propagation delay, jitter, and other signal parameters that can impact timing consistency. |

| Component Interface Signals | Use eye diagrams to evaluate digital signals and how signals transition between states. |

| Connector/Cable Signals | Ensuring impedance matching through connectors and cables is crucial to signal transfer quality and strength. |

As shown in the table above, many important PCB signal integrity simulation concerns apply to multiple signal types. For example, following good trace routing guidelines that emphasize spacing and trace length minimization can be generally applied. Impedance is also a major concern for all signals, either matching to ensure maximum signal transfer or minimization to ensure adequate signal strength. In some cases, especially interconnection via connector or cable, it is important to know and follow the applicable signal integrity compliance standard(s).

Optimizing PCB Signal Integrity Simulation

Ensuring signal integrity is a primary determinant of how well your board meets its performance objectives. Failing to do so effectively renders the design useless without redesign or remanufacture, leading to unnecessary additional costs. The best way to ensure that your board achieves its signal quality requirements and minimizes degradation effects, such as electromagnetic interference (EMI), is to employ effective simulation. The keys to maximizing the process and benefits of simulation are as follows:

Keys to PCB Signal Integrity Simulation Optimization

🔑 Identify the different signal types on your board to analyze.

🔑 Clearly define the performance objective(s) for each signal type to analyze.

🔑 Select simulation software tool(s) based on signal type(s).

🔑 Accurately model components and board elements based on software tool requirements.

🔑 Leverage mathematical and graphical analyses to evaluate signal performance.

🔑 Make design changes, as necessary, to ensure your design meets signal integrity goals.

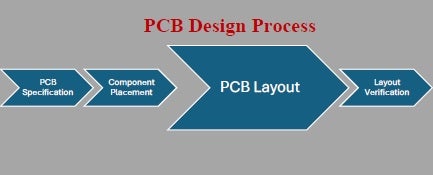

The first step to effectively using simulation is to choose the best software tool based on your design requirements. In many cases, a general comprehensive simulation program like Sigrity may be utilized for all of your simulation needs. Depending upon the complexity of your design, however, different programs with dedicated advanced capabilities may also be necessary. For example, in-depth thermal analysis or CFD evaluation. The importance of matching your software choice with your PCB signal integrity simulation needs lends to partnering with an industry expert with decades of experience supplying engineers with the best tool for design success.

EMA Design Automation is a leading provider of the resources that engineers rely on to accelerate innovation. We provide solutions that include PCB design and analysis packages, custom integration software, engineering expertise, and a comprehensive academy of learning and training materials, which enable you to create more efficiently. For more information on PCB signal integrity simulation solutions and how we can help you or your team innovate faster, contact us.